# IPC/COMPACT6-1A - IPC/NETSBC-6A

Document Ordercode: DOC/COMPACT6-SLE

| Revision | Date       | Author      | Modification                             |

|----------|------------|-------------|------------------------------------------|

| 0.1      | 23.09.2008 | R. Newbould | Preliminary release                      |

| 0.2      | 10.10.2008 | R. Newbould | Mechanical data added                    |

| 1.0      | 29.07.2009 | R. Newbould | First release                            |

| 1.1      | 16.03.2010 | R. Newbould | Minor corrections                        |

| 1.2      | 16.06.2010 | R. Newbould | Minor correction                         |

| 1.3      | 22.10.2013 | R. Newbould | Description of power fail function added |

|          |            |             |                                          |

|          |            |             |                                          |

|          |            |             |                                          |

|          |            |             |                                          |

|          |            |             |                                          |

|          |            |             |                                          |

|          |            |             |                                          |

|          |            |             |                                          |

# **Contents**

| 1 | Intro | duction  |                                         | 7  |

|---|-------|----------|-----------------------------------------|----|

|   | 1.1.  | Genera   | al Remarks                              | 7  |

|   | 1.2.  | Conten   | nts of this Documentation               | 7  |

|   | 1.3.  | Namin    | g Conventions                           | 7  |

|   | 1.4.  | Additio  | onal Products and Documents             | 7  |

|   |       | 1.4.1.   | Hardware Products                       | 7  |

|   |       | 1.4.2.   | Software Products                       | 8  |

|   | 1.5.  | Docum    | nents and References                    | 8  |

|   |       | 1.5.1.   | Syslogic Documentation                  | 8  |

|   |       | 1.5.2.   | Standards and Books                     | 8  |

|   |       | 1.5.3.   | Datasheets                              | 8  |

|   | 1.6.  | Items d  | lelivered                               | 9  |

|   | 1.7.  | Installa | ation                                   | 9  |

|   | 1.8.  | Safety   | Recommendations and Warnings            | 9  |

|   | 1.9.  | Electro  | o-Static Discharge                      | 9  |

|   | 1.10. | Life Cy  | ycle Information                        | 9  |

|   |       | 1.10.1.  | Transportation and Storage              | 9  |

|   |       | 1.10.2.  | Operation                               | 10 |

|   |       | 1.10.3.  | Maintenance and Repair                  | 10 |

|   |       | 1.10.4.  | Warranty                                | 10 |

|   |       | 1.10.5.  | RoHS                                    | 10 |

|   |       | 1.10.6.  | Disposal and WEEE                       | 10 |

| 2 | Produ | ıct Desc | ription                                 | 11 |

|   | 2.1.  | IPC/CC   | OMPACT-SL System                        | 11 |

|   | 2.2.  | Feature  | es of the IPC/NETSBC-6A                 | 11 |

|   | 2.3.  | Operati  | ing Modes                               | 15 |

|   | 2.4.  | Startup  | Modes                                   | 15 |

| 3 | Hard  | ware De  | escription                              | 16 |

|   | 3.1.  | Overvi   | ew                                      | 16 |

|   | 3.2.  | Memor    | ry and I/O Resources                    | 18 |

|   |       | 3.2.1.   | General Memory Layout and Configuration | 18 |

|   |       | 3.2.2.   | General I/O Layout and Configuration    | 20 |

|   | 3.3.  | AMD (    | Geode LX800 CPU                         | 22 |

|   | 3.4.  | AMD (    | CS5536 Companion Chip                   | 22 |

|   | 3.5.  | PCI De   | evices                                  | 23 |

|   | 3.6.  | Hardwa   | are Interrupts                          | 24 |

|   | 3.7.  | Periphe  | eral Devices                            | 24 |

|   |       | 3.7.1.   | Scope                                   | 24 |

|   |       | 3.7.2.   | Socket Memory                           | 24 |

|   |       | 3.7.3.   | VGA Interface                           | 26 |

|   |       | 3.7.4.   | DVI Interface                 | 26 |

|---|-------|----------|-------------------------------|----|

|   |       | 3.7.5.   | IDE/CompactFlash-Interface    | 28 |

|   |       | 3.7.6.   | Serial Ports 1/2              | 30 |

|   |       | 3.7.7.   | USB Interface                 | 30 |

|   |       | 3.7.8.   | PS/2 Keyboard/Mouse Interface | 31 |

|   |       | 3.7.9.   | Ethernet Interfaces           | 32 |

|   |       | 3.7.10.  | Watchdog                      | 33 |

|   |       | 3.7.11.  | Power Supply                  | 33 |

|   |       | 3.7.12.  | Power supervision             | 34 |

|   |       | 3.7.13.  | Power Fail                    | 34 |

|   |       | 3.7.14.  | Remote On/Off                 | 36 |

|   |       | 3.7.15.  | Configurations Switches       | 38 |

|   |       | 3.7.16.  | Factory Programming Header    | 39 |

|   |       | 3.7.17.  | LPC Header                    | 39 |

|   |       | 3.7.18.  | Isolated Power Supply         | 39 |

|   | 3.8.  | Optiona  | al Functions                  | 39 |

|   | 3.9.  | Hardwa   | are Limitations               | 40 |

|   |       | 3.9.1.   | PCI Bus Limitations           | 40 |

|   |       | 3.9.2.   | ISA Bus Limitations           | 40 |

| 4 | Progr | ramming  | Information                   | 41 |

|   | 4.1.  | Overvie  | ew                            | 41 |

|   | 4.2.  | Interrup | pt, Memory and I/O Resources  | 41 |

|   |       | 4.2.1.   | Interrupt Resources           | 41 |

|   |       | 4.2.2.   | Memory Resources              | 41 |

|   |       | 4.2.3.   | I/O Resources                 | 41 |

|   | 4.3.  | Periphe  | eral Devices                  | 51 |

|   |       | 4.3.1.   | VGA-Interface                 | 51 |

|   |       | 4.3.2.   | IDE-Interface                 | 51 |

|   |       | 4.3.3.   | Serial Ports                  | 51 |

|   |       | 4.3.4.   | Keyboard/Mouse Interface      | 51 |

|   |       |          | Ethernet Interfaces           | 52 |

|   |       | 4.3.6.   | Temperature Sensor            | 52 |

|   |       | 4.3.7.   | Watchdog                      | 52 |

| 5 | Enclo | sure, As | sembly and Mounting           | 54 |

|   | 5.1.  | IPC/CO   | DMPACT6-SL Dimensions         | 54 |

|   | 5.2.  | Internal | l Cabling                     | 54 |

|   | 5.3.  | Service  | able Parts                    | 54 |

|   | 5.1.  | Final M  | Iounting of the Enclosure     | 57 |

|   |       | 5.1.1.   | Rear Mounting                 | 57 |

|   |       | 5.1.2.   | Vertical Bottom Mounting      | 58 |

|   |       | 5.1.3.   | Horizontal Bottom mounting    | 59 |

|   |       | 5.1.4.   | DIN Rail Mounting             | 60 |

| 6  | Insta | llation and Cabling                     | 61 |

|----|-------|-----------------------------------------|----|

|    | 6.1.  | Introduction                            | 61 |

|    | 6.2.  | Powering the IPC/COMPACT-SL System      | 61 |

|    | 6.3.  | Cabling the Interfaces                  | 63 |

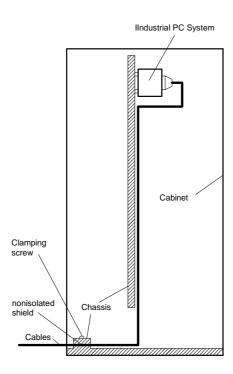

|    | 6.4.  | Grounding                               | 64 |

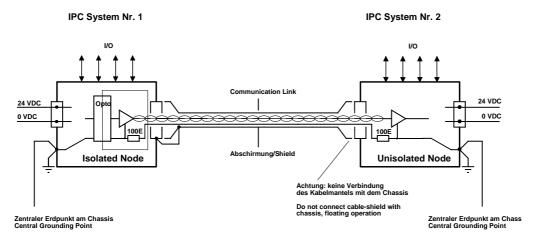

|    | 6.5.  | Cabling of Communication Links          | 64 |

| 7  | Techi | nical Data                              | 66 |

|    | 7.1.  | Electrical Data                         | 66 |

|    | 7.2.  | EMI / EMC Specification                 | 69 |

|    |       | 7.2.1. Relevant Standards               | 69 |

|    |       | 7.2.2. Emission                         | 69 |

|    |       | 7.2.3. Immunity                         | 70 |

|    | 7.3.  | Environmental Specification             | 70 |

|    | 7.4.  | Mechanical Data                         | 71 |

| 8  | Firmv | ware                                    | 73 |

|    | 8.1.  | Software Structure                      | 73 |

|    | 8.2.  | Firmware Functions                      | 73 |

|    | 8.3.  | Application Programming Interface (API) | 73 |

|    | 8.4.  | Operating Systems                       | 74 |

| 9  | Prod  | uct Revision History                    | 75 |

|    | 9.1.  | Hardware                                | 75 |

|    | 9.2.  | Firmware                                | 75 |

| 10 | Manu  | ıfacturer Information                   | 76 |

|    | 10.1. | Contact                                 | 76 |

# **List of Tables**

| Tab. 1  | Physical Memory Address Space Layout                         | 18 |

|---------|--------------------------------------------------------------|----|

| Tab. 2  | I/O Address Space Layout                                     | 21 |

| Tab. 3  | PCI Devices                                                  | 23 |

| Tab. 4  | Hardware Interrupt Table                                     | 24 |

| Tab. 5  | Socket Memory Configuration                                  | 25 |

| Tab. 6  | DVI-D connector P5                                           | 27 |

| Tab. 7  | IDE Configuration Options                                    | 28 |

| Tab. 8  | IDE Connector P7 (2x22 pin)                                  | 29 |

| Tab. 9  | Serial Ports COM1 and COM2                                   | 30 |

| Tab. 10 | USB Interface Connector J10 (2x5pin)                         | 31 |

| Tab. 11 | Keyboard/Mouse Configuration Options                         | 31 |

| Tab. 12 | Keyboard/Mouse internal Header J6 (2x5 pin)                  | 32 |

| Tab. 13 | Ethernet Twisted Pair Interface Connector P18 and P19 (RJ45) | 33 |

| Tab. 14 | Watchdog Configuration Options                               | 33 |

| Tab. 16 | Power Supervision Configuration Options                      | 33 |

| Tab. 17 | Power plane short circuit                                    | 34 |

| Tab. 18 | PCU timing configuration through S14                         | 36 |

| Tab. 19 | Power Fail                                                   | 38 |

| Tab. 20 | Remote On/Off                                                | 38 |

| Tab. 21 | Factory Programming Header J5 (2x5 pin)                      | 39 |

| Tab. 22 | LPC J3 (1x7 pin)                                             | 39 |

| Tab. 23 | NETSBC-6A System Registers                                   | 42 |

| Tab. 24 | TRIGGER* Source Selection                                    | 45 |

| Tab. 25 | I2C Address Space                                            | 52 |

| Tab. 26 | Power supply connector P1 (2x2 pin, product version #4.x)    | 61 |

| Tab. 27 | Power supply connector P1 (1x3 pin, product version #1-3)    | 61 |

| Tab. 28 | Weidmüller power connector                                   | 62 |

| Tab. 29 | IPC/COMPACT6-1E: Connectors                                  | 63 |

| Tab. 30 | General Absolute Maximum Ratings                             | 66 |

| Tab. 31 | General Recommended Operating Conditions                     | 67 |

| Tab. 32 | General Electrical Characteristics                           | 67 |

| Tab. 33 | General Switching Characteristics                            | 68 |

| Tab. 34 | Electromagnetic Emission                                     | 69 |

| Tab. 35 | Electromagnetic Immunity                                     | 70 |

| Tab. 36 | Coordinates                                                  | 71 |

| Tab. 37 | Hardware Revision State                                      | 75 |

# **List of Figures**

| Fig. 1  | Block Diagram (IPC/NETSBC-6A)                                             | 14      |

|---------|---------------------------------------------------------------------------|---------|

| Fig. 2  | Board Layout (NETSBC-6X)                                                  | 17      |

| Fig. 3  | Memory Map (IPC/NETSBC-6A board)                                          | 19      |

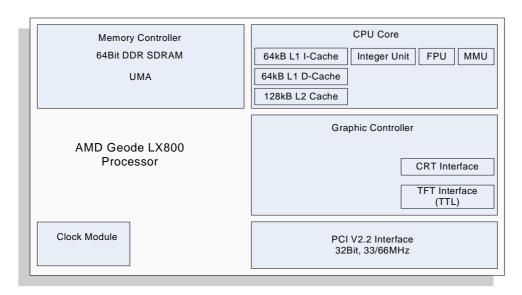

| Fig. 4  | AMD Geode LX800 processor                                                 | 22      |

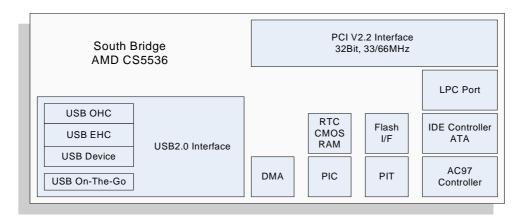

| Fig. 5  | AMD Geode CS5536 companion chip                                           | 22      |

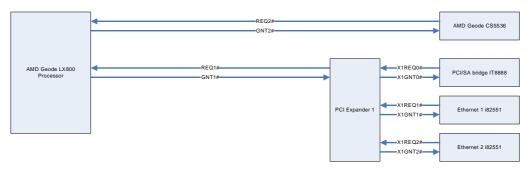

| Fig. 6  | PCI System                                                                | 23      |

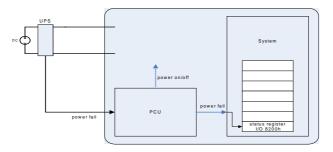

| Fig. 7  | Typical power fail application                                            | 34      |

| Fig. 8  | Typical power fail flow                                                   | 35      |

| Fig. 9  | Application example: CAR PC                                               | 36      |

| Fig. 10 | Startup timing diagram                                                    | 37      |

| Fig. 11 | Shutdown timing diagram                                                   | 37      |

| Fig. 12 | Watchdog Blockdiagram                                                     | 53      |

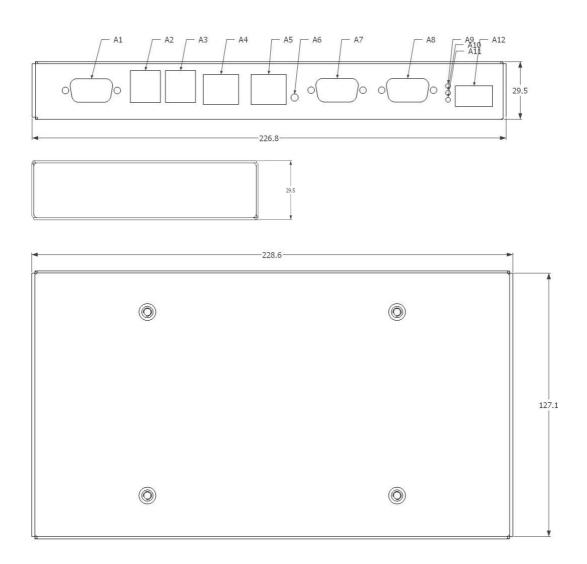

| Fig. 13 | IPC/COMPACT6-1A                                                           | 54      |

| Fig. 14 | Service of battery or Compact Flash card                                  | 56      |

| Fig. 15 | Rear mounting of the IPC/COMPACT6-SL (product image may vary)             | 57      |

| Fig. 16 | Vertical bottom mounting of the IPC/COMPACT6-SL (product image may va     | ary).58 |

| Fig. 17 | Horizontal bottom mounting of the IPC/COMPACT6-SL (product image ma 59    | y vary) |

| Fig. 18 | One possible way of mounting the IPC/COMPACT6-SL onto the DIN-Rail        | 60      |

| Fig. 19 | Front view with connector markings                                        | 63      |

| Fig. 20 | Additional grounding of the cable shields at the entry point of a cabinet | 64      |

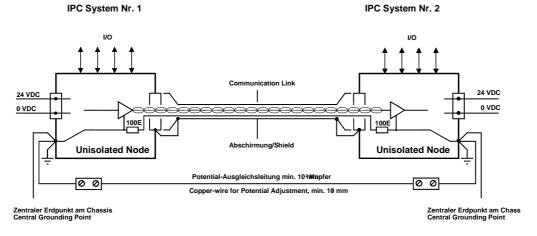

| Fig. 21 | Non isolated communication link with common chassis potential             | 65      |

| Fig. 22 | Isolated communication link                                               | 65      |

| Fig. 23 | Three side view of the IPC/COMPACT6-SL enclosure (front, side, bottom)    | 72      |

# 1 Introduction

## 1.1. General Remarks

The content and presentation of this document has been carefully checked. No responsibility is accepted for any errors or omissions in the documentation.

Note that the documentation for the products is constantly revised and improved. The right to change this documentation at any time without notice is therefore reserved.

Syslogic is grateful for any help referring to errors or for suggestions for improvements.

The following registered trademarks are used:

$\begin{array}{ll} IBM\text{-PC, PC/AT, PS/2} & trademarks of IBM Corporation \\ I^2C & trademark of Philips Corporation \\ CompactFlash & trademark of SanDisk Corporation \\ DiskOnChip & registered trademark of M-Systems LTD \end{array}$

PC/104 trademark of PC/104 Consortium PCI/104 trademark of PC/104 Consortium

Geode trademark of Advanced Micro Devices (AMD)

Windows CE trademark of Microsoft Corporation

Windows XP Embedded trademark of Microsoft Corporation

#### 1.2. Contents of this Documentation

This document addresses to system integrators, programmers and instructed installation and maintenance personal working with the system. It provides all information needed to configure, setup and program the IPC/COMPACT6-1A system.

#### 1.3. Naming Conventions

The exact product identification is IPC/COMPACT6-1A. Throughout this documentation the product is reference through it's marketing name "IPC/COMPACT6-SL".

The same applies to the integrated base board. The exact board identification is IPC/NETSBC-6A. Throughout this documentation it will be referenced as "NETSBC-6A".

#### 1.4. Additional Products and Documents

#### 1.4.1. Hardware Products

In order to mount the IPC/COMPACT7-SL correctly there are four different mounting kits which have to be ordered separately:

- IPC/MKITCP-1A: for rear mounting (DOC/IPC\_MKITCP-1AE)

- IPC/MKITCP-2A: for bottom mounting (DOC/IPC\_MKITCP-2AE)

- IPC/MKITCP-2C: for bottom mounting (DOC/IPC\_MKITCP-2CE)

- IPC/MKITCP-2E: DIN rail kit (DOC/IPC\_MKITCP-2EE)

For further assistance and information please contact the manufacturer.

#### 1.4.2. Software Products

The following software products are useful together with the NETSBC-6A processor board:

- IPC/NETIPCFW-6A: Firmware for NETSBC-6A boards (contact manufacturer)

- IPC/IOCOMSW-1A: Sample program code and utilities for x86 based PC/104 systems

- Operating Systems: check chapter 6.4 for a list of supported implementations.

#### 1.5. Documents and References

#### 1.5.1. Syslogic Documentation

The following documents are *required* for correct installation and operation of the IPC/COMPACT6-SL:

- DOC/NETIPCFW6-E: User Documentation for NETIPC Firmware (contact manufacturer)

- DOC/IPC\_IOCOMSW-E: User Documentation for programming examples and utilities

#### 1.5.2. Standards and Books

The following documents are useful for additional information about PC/104 and IEEE 996.1:

- PC/104 Specification Version 2.3

- PCI/104 Specification Version 1.0

- IEEE 996: IEEE standard document 'Personal Computer Bus Standard'

- IEEE 996.1: IEEE standard document 'Compact Embedded-PC Modules'

The PC/104 Specification may be downloaded from the Internet (see address below).

- PC/104 Consortium www.pc104.org

The IEEE standard documents may be ordered directly from the IEEE or any standards document distributor (see addresses below).

- IEEE Standards Department www.ieee.org

- 'ISA & EISA, Theory and Operation' by Edward Solari (Annabooks, San Diego), ISBN 0-929392-15-9

- 'PCI System Architecture' by Tom Shanley / Don Anderson (Mindshare, Inc.), ISBN 0-201-30974-2

#### 1.5.3. Datasheets

- Datasheet AMD Geode LX800 microprocessor

<a href="http://www.amd.com/us-en/ConnectivitySolutions/ProductInformation/0,.50">http://www.amd.com/us-en/ConnectivitySolutions/ProductInformation/0,.50</a> 2330 9863 13022%5E13073,00.ht

- Datasheet AMD CS5536 companion chip http://www.amd.com/us

$\frac{en/ConnectivitySolutions/ProductInformation/0, 50\_2330\_9863\_13022\%5E130}{54\%5E13083,00.html}$

- Datasheet Intel 82551ER Fast Ethernet Controller

<a href="http://www.intel.com/design/network/products/lan/docs/82551ER\_docs.htm">http://www.intel.com/design/network/products/lan/docs/82551ER\_docs.htm</a>

- Datasheet Intel 82551IT Fast Ethernet Controller

<a href="http://www.intel.com/design/network/products/lan/docs/82551it\_docs.htm">http://www.intel.com/design/network/products/lan/docs/82551it\_docs.htm</a>

#### 1.6. Items delivered

The IPC/COMPACT6-SL comes with an IPC/NETSBC-6A base board and an enclosure.

#### 1.7. Installation

The firmware configuration and download is described in the appropriate firmware documentation.

#### **Important Note**

Before applying power to the IPC/COMPACT6-SL system, the NETSBC-6A board must be configured correctly and mounted.

# 1.8. Safety Recommendations and Warnings

The products are intended for measurement, control and communications applications in industrial environments. The products must be assembled and installed by specially trained people. The strict observation of the assembly and installation guidelines is mandatory.

The use of the products in systems in which life or health of persons is directly dependent (e.g. life support systems, patient monitoring systems, etc.) is not allowed.

The use of the products in potentially explosive atmospheres requires additional external protection circuitry which is not provided with the products.

In case of uncertainty or of believed errors in the documentation please immediately contact the manufacturer (address see chapter 10). Do not use or install the products if you are in doubt. In any case of misuse of the products, the user is solely liable for the consequences.

#### 1.9. Electro-Static Discharge

Electronic boards are sensitive to Electro-Static Discharge (ESD). Please ensure that the product is handled with care and only in a ESD protected environment. Otherwise a proper operation is not garanteed and the warranty is not applicable.

# 1.10. Life Cycle Information

## 1.10.1. Transportation and Storage

During transportation and storage the products must be in their original packing. The original packing contains a box with antistatic and shock-absorbing material. It is recommended, to keep the original packing in case of return of the product to the factory for repair. Note that the packing is recyclable.

#### 1.10.2. Operation

The operating environment must guarantee the environmental parameters (temperature, power supply, etc.) specified in the technical specification section of the product manuals.

The main functionality of the IPC system is defined by the application programs running on the processor board. The operating system and application programs are not part of the delivery by Syslogic but are defined, developed and tested by the customer or a system-integrator for each specific application. Refer to the respective documentation for more information.

#### 1.10.3. Maintenance and Repair

The IPC system features error- and malfunction-detection circuitry. Diagnostic information gathered is transferred to the applications software where it can be used. In the rare case of a module hardware-failure or malfunction, the complete board should be exchanged. The faulty board must be returned to the factory for repair. Please use whenever possible the original packing for return of the product (ESD and mechanical protection).

#### 1.10.4. Warranty

Our products are covered by a world-wide manufacturers warranty. The warranty period starts at the delivery time from our official distributor to the customer. The duration of the warranty period is specified in the respective product catalogs and the offers. All products carry a serial number for identification. The manufacturing data and deliveries are registered in a high level Quality Management System.

The warranty covers material and manufacturing defects. All products must be returned via the official distributor to the factory for repair or replacement. The warranty expires immediately if the products are damaged of operation outside of the specified recommended operating conditions. The warranty also expires if the date code or job number listed on the product is altered or rendered unintelligible. The warranty does not include damage due to errors in firmware or software delivered with the products.

#### 1.10.5. RoHS

The products of the IPC/COMPACT6-SL family are designed and produced according to the Restriction of Hazardous Substances (RoHS) Directive (2002/95/EC).

#### 1.10.6. Disposal and WEEE

At the end of the life span the IPC products must be properly disposed. IPC products contain a multitude of elements and must be disposed like computer parts. Some of the IPC products contain batteries which should be properly disposed.

The products of the IPC/COMPACT6-SL are not designed ready for operation for the end-user and intended for consumer applications. Therefore the Waste Electrical and Electronic Equipment (WEEE) Directive (2002/96/EC) is not applicable. But users should still dispose the product properly at the end of life.

# 2 Product Description

# 2.1. IPC/COMPACT-SL System

The IPC/COMPACT6-SL contains an enclosure and the IPC/NETSBC-6A motherboard. A list of main features of the motherboard can be found below:

# 2.2. Features of the IPC/NETSBC-6A

#### CPU Core

- AMD Geode LX800 @ 0.9W low power industrial processor board eliminating the need for enforced cooling

- high performance 32-bit 8-stage pipeline x86 based processor core with efficient prefetch and branch prediction

- integrated Floating Point Unit (supports MMX and AMD 3Dnow! instruction sets

- 500MHz processor clock

- Split I/D L1 cache\_64kB Instruction cache, 64kB Data cache

- Configurable L2 cache (I or D or both)

- 64-bit wide DDR SDRAM interface

#### Memory

- 512 Mbyte DRAM on board (DDR400, 200MHz)

# Graphics Controller

- high performance 2D 64-bit graphics controller with backwards compatibility to VGA and SVGA standards

- CRT controller supporting up to 1920x1440x32 bpp at 85Hz and 1600x1200x32 bpp at 100Hz

#### CompactFlash and IDE Interface

- Enhanced IDE interface (ATA-5 specification) supporting 2 IDE devices with PIO modes 0 to 4, MDMA modes 0 to 2 or UDMA modes 0 to 5

- standard 44 pin IDE (2mm) connector for two external IDE devices

- CompactFlash Type I connector for onboard mountable CompactFlash card configurable as master or slave IDE device (replacing one of the external IDE devices)

#### Integrated Peripherals

- integrated peripheral controller (IPC) with PC/AT compatible DMA controllers (2 x 8237), interrupt controllers (2 x 8259) and timer/counter channels (8254)

- hardware watchdog configurable for 100 ms or 1.6 s timeout, hardware reset activation

- temperature supervisor for software controlled power management

#### PS/2 Mouse and Keyboard Interface

- PC/AT compatible keyboard controller (8242 compatible) with PS/2 mouse support

- Only available on an internal header

#### Serial Ports

- Two serial RS232 ports (COM1, COM2) with 16 byte receive and transmit fifo (16550)

#### Universal Serial Bus

- Four USB V2.0 ports (OHCI/EHCI-Host Controller)

#### Ethernet

- Two 10/100baseT Ethernet interfaces

#### Firmware Flash Memory

16 MBit BootBlock Flash for BIOS, BIOS extensions and 1.44 Mbyte ROMdrive A: (floppy replacement), supporting easy firmware update through serial port

#### Add-On Memory

- 32 pin DIL socket for user installable Socket Memory supporting various types of 32 and 28 pin SRAM and EEPROM devices from 32 kbyte up to 512 kbyte

- battery backed through onboard battery or header

#### Real Time Clock

- Year 2000 compliant Real Time Clock (PC/AT compatible)

- battery backed through onboard battery or header

#### Configuration Switches

- Two rotary hex switches for customer application

# Power Supply

- Onboard non-isolated power supply with wide input range (10Vdc ... 30Vdc)

- Configurable power supply supervision (this function is only available on systems with revision 3 or higher)

- Monitors either external power supply voltage or it can be used as external power fail or on/off input (this function is only available on systems with revision 3 or higher)

- Optional isolated power supply

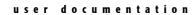

Fig. 1 Block Diagram (IPC/NETSBC-6A)

# 2.3. Operating Modes

The IPC/COMPACT6-SL resp. NETSBC-6A is based on the standard PC/AT architecture and therefore operates in DOS-compatible mode (real mode) on start up. The configurable BIOS initializes all onboard peripherals to their default values, executes the BIOS extensions programmed into the onboard Boot Block Flash by the user and BIOS extensions found on installed expansion boards prior to booting the operating system from a user-selectable drive (boot sector or OS image file). The operating system (or eventually a BIOS extension) may switch to protected mode to execute high performance 32-bit program code.

# 2.4. Startup Modes

The NETSBC-6A doesn't support any special startup modes.

# **3 Hardware Description**

# 3.1. Overview

The NETSBC-6A board hardware may be configured by software (BIOS) and by jumper setting. Software configuration should always be done using the BIOS configuration program freely available as part of the NETSBC-6A firmware package IPC/NETIPCFW-6A, unless the BIOS does not support it (see firmware documentation DOC/NETIPCFW6 for details about supported BIOS configuration options).

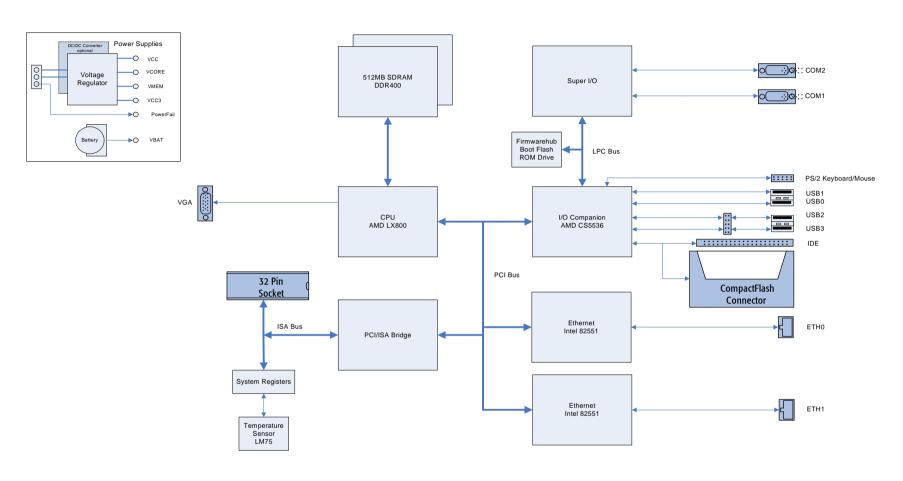

The jumper and connector locations are shown in the board layout drawing (Fig. 3).

#### **Important Note**

Always check the jumper configuration of a freshly received board to comply with your system requirements before applying power, otherwise the system may get damaged or may fail to operate.

Fig. 2 Board Layout (NETSBC-6X)

# 3.2. Memory and I/O Resources

#### 3.2.1. General Memory Layout and Configuration

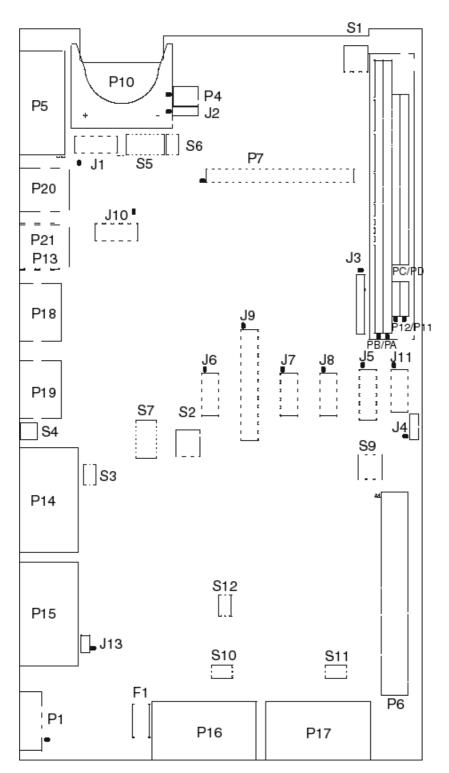

The NETSBC-6A uses the same memory layout as a standard desktop PC. Four onboard devices, DRAM, graphics controller, Boot Block Flash and Socket Memory, make use of the 4 GByte adressable memory space.

| Address               | Device / Register                | Remarks                       |

|-----------------------|----------------------------------|-------------------------------|

| 0000'00000009'FFFFh   | 640 kByte Main Memory (DRAM)     |                               |

| 000A'0000000B'FFFFh   | Video Memory                     |                               |

| 000C'0000000D'BFFFh   | Configurable memory range (BIOS, | see paragraph 3.7.1 and 4.2.3 |

|                       | BIOS Extensions, DRAM, Socket    |                               |

|                       | Memory or redirected to PC/104   |                               |

|                       | bus)                             |                               |

| 000D'C000000F'FFFFh   | BIOS                             | do not write                  |

| 0010'000001EAF'FFFFh  | 491 Mbyte Main Memory (DRAM)     | free Memory above 1M          |

| 01EB0'00001FAF'FFFFh  | 16MB Graphic Memory              | do not access                 |

| 01FB0'000001FFF'FFFFh | 4MB SMM, Firmbase, VSA           | do not access                 |

| 8088'000083EF'FFFFh   | Reserved                         | do not access                 |

| FFE0'0000FFF7'FFFFh   | 1.44 Mbyte Firmware Flash        | ROM drive                     |

| FFF8'0000FFFF'FFFh    | BIOS/BIOS Extensions             | do not access                 |

Tab. 1 Physical Memory Address Space Layout

#### **Important Note**

The main memory above 1M isn't fully usable for applications. The main memory for applications is shared with the graphics memory (UMA: Unified Memory Architecture). The graphics memory can be configured from 4MB to 60MB. The default value is 16MB.

Firmbase and System Management Mode software and drivers for Geode's VSA (Virtual System Architecture) are located at the top of the extended memory range (e.g. 4MB). The graphic memory Size can configured in the BIOS. To calculate the remaining memory space the graphic memory size and 4MB of the Firmbase/SMM/VSA must be subtracted from the memory top.

IPC/NETSBC-6A example: With the graphics memory size of 16 MByte (default), usable main memory ends at address:

- 01EAF'FFFh (492 Mbyte free main memory)

This must be considered in operating system configuration (e.g. Windows CE).

Depending on Shadowing configuration the effective size may be slightly higher.

Fig. 3 Memory Map (IPC/NETSBC-6A board)

# 3.2.2. General I/O Layout and Configuration

The NETSB's 64 kbyte I/O address space is mapped to the PC/104 bus address space as indicated in the table below. Note that 16 bit address decoding should be used on all PC/104 expansion boards to make efficient use of the I/O address space.

| Address     | Device / Register               | Remarks              |

|-------------|---------------------------------|----------------------|

| 0000000Fh   | Slave DMA                       |                      |

| 0020h       | PIC Master – Command/Status     |                      |

| 0021h       | PIC Master – Command/Status     |                      |

| 00400043h   | PIT                             |                      |

| 0060h       | Keyboard/Mouse – Data Port      |                      |

| 0061h       | Port B Control                  |                      |

| 0064h       | Keyboard/Mouse - Command/Status |                      |

| 0070.0.071h | RTC RAM Addres/Data Port        |                      |

| 00720073h   | High RTC RAM Address/Data Port  |                      |

| 0080h       | Post Code Display               |                      |

| 00810083h   | DMA Low Page                    |                      |

| 0087h       | DMALow Page                     |                      |

| 0089008Bh   | DMA Low Page                    |                      |

| 008Fh       | DMA Low Page                    |                      |

| 0092h       | Port A                          |                      |

| 00A0h       | PIC Slave - Command/Status      |                      |

| 00A1h       | PIC Slave - Command/Status      |                      |

| 00C0h       | Master DMA                      |                      |

| 00C2h       | Master DMA                      |                      |

| 00C4/00C6h  | Master DMA                      |                      |

| 00C8/00CA   | Master DMA                      |                      |

| 00CCh       | Master DMA                      |                      |

| 00CEh       | Master DMA                      |                      |

| 00D0h       | Master DMA                      |                      |

| 00D2h       | Master DMA                      |                      |

| 00D4h       | Master DMA                      |                      |

| 00D6h       | Master DMA                      |                      |

| 00D8h       | Master DMA                      |                      |

| 00DAh       | Master DMA                      |                      |

| 00DCh       | Master DMA                      |                      |

| 00DEh       | Master DMA                      |                      |

| 0200023Fh   | free                            | avail. on PC/104 bus |

| 0278027Fh   | Reserved for LPT2               |                      |

| 02E002E7h   | free                            | avail. on PC/104 bus |

| 02E802Efh   | free                            | avail. on PC/104 bus |

| 02F802FFh   | COM2                            |                      |

| 0300033Fh   | free                            | avail. on PC/104 bus |

| 0340036Fh   | free                            |                      |

| 03700372h   | Reserved for Floppy 2                         |                      |

|-------------|-----------------------------------------------|----------------------|

| 374375h     | Reserved for Floppy 2                         |                      |

| 0377h       | Reserved for Floppy 2                         |                      |

| 0378037Fh   | Reserved for LPT1                             |                      |

| 03B003BBh   | VGA Registers (MDA)                           |                      |

| 03BC03BFh   | Reserved for LPT3                             |                      |

| 03C003CFh   | VGA registers (EGA)                           |                      |

| 03D003DFh   | VGA registers (CGA)                           |                      |

| 03E003E7h   | free                                          |                      |

| 3E803EFh    | free                                          | avail. on PC/104 bus |

| 03F0.0.3F2h | Reserved for Floppy 1                         |                      |

| 03F403F5h   | Reserved for Floppy 1                         |                      |

| 03F6h03F7h  | Primary IDE Channel                           |                      |

| 03F7h       | Reserved for Floppy 1                         |                      |

| 03F803FFh   | COM1                                          |                      |

| 04810483h   | DMA High Page                                 |                      |

| 0487h       | DMA High Page                                 |                      |

| 0489048Bh   | DMA High Page                                 |                      |

| 048Fh       | DMA High Page                                 |                      |

| 04D0h       | PIC Level/Edge                                |                      |

| 04D1h       | PIC Level Edge                                |                      |

| 050007FF    | Runtime Registers Super I/O                   |                      |

| 0A78h       | Plug'n Play configuration port                |                      |

| 0CF80CFFh   | PCI configuration registers                   |                      |

| 760076FFh   | free                                          | avail. on PC/104 bus |

| 770077FFh   | free                                          | avail. on PC/104 bus |

| 8200821Fh   | NETSBC-6A system registers                    |                      |

| 8220827Fh   | free                                          | avail. on PC/104 bus |

| 0D0000EFFFh | reserved for PCI devices (VGA, Ethernet, USB, |                      |

|             | IDE)                                          |                      |

| -           |                                               |                      |

Tab. 2 I/O Address Space Layout

Only the I/O addresses which are marked with "avail. On PC/104 bus" can be accessed on the aforementioned connector and be used for additional peripherals. The other unused I/O space can't be accessed because these cycles are claimed by the integrated South Bridge and not by the PCI/ISA Bridge.

# 3.3. AMD Geode LX800 CPU

The AMD Geode LX processors are highly integrated x86 processors for embedded applications. The LX800 integrates the core microprocessor and the north bridge into one device.

Fig. 4 AMD Geode LX800 processor

# 3.4. AMD CS5536 Companion Chip

The AMD Geode CS5536 companion device is designed to work with the LX800 microprocessor.

Fig. 5 AMD Geode CS5536 companion chip

# 3.5. PCI Devices

All devices follow the PCI 2.2 specification. The BIOS (and/or OS) control memory and I/O resources.

Fig. 6 PCI System

| PCI Device (IDSEL)    | Device ID | PCI IRQ       | REQ / GNT       | Comment               |

|-----------------------|-----------|---------------|-----------------|-----------------------|

| Host Bridge           | 2080h     | n/a           | 2               | Integrated in chipset |

| Graphic Controller    | 2081h     | INTA# (IRQ9)  | n/a             | Integrated in chipset |

| Encryption Controller | 2082h     | INTA# (IRQ9)  | n/a             | Integrated in chipset |

| Ethernet Controller 2 | 1209h     | INTB# (IRQ10) | 1 <b>→</b> X1-0 | Intel 82551           |

| (AD22)                |           |               |                 |                       |

| Ethernet Controller 1 | 1209h     | INTB# (IRQ10) | 1 <b>→</b> X1-1 | Intel 82551           |

| (AD23)                |           |               |                 |                       |

| PCI/ISA bridge (AD24) | 0628h     | n/a           | 1 <b>→</b> X1-2 | IT8888                |

| PCI/ISA bridge        | 2090h     | n/a           | n/a             | Integrated in chipset |

| IDE Controller        | 209Ah     | n/a           | n/a             | Integrated in chipset |

| Audio Controller      | 2093h     | INTA# (IRQ9)  | n/a             | Integrated in chipset |

| USB Controller        | 2094h     | INTD# (IRQ7)  | n/a             | Integrated in chipset |

| USB Controller        | 2095h     | INTD# (IRQ7)  | n/a             | Integrated in chipset |

Tab. 3 PCI Devices

# 3.6. Hardware Interrupts

The AMD Geode LX800 chipset integrates two legacy 8259-compatible Programmable Interrupt Controllers (PIC). The registers of the PIC can be accessed through the I/O ports 020h and 021h resp. 0A0h and 0A1h.

| Device             | IRQ | PCI IRQ   | Comment                                     |

|--------------------|-----|-----------|---------------------------------------------|

| 8254 Timer         | 0   | -         | Legacy                                      |

| Keyboard           | 1   | -         | Legacy                                      |

| 8259               | 2   | -         | Slave controller                            |

| UART               | 3   | -         | COM2                                        |

| UART               | 4   | -         | COM1                                        |

| Free               | 5   | -         | Available on PC/104 bus                     |

| Free               | 6   | -         | Available on PC/104 bus                     |

| USB                | 7   | PCI INTC# | Do not used for with other devices          |

|                    |     | PCI INTD# |                                             |

| RTC                | 8   | -         | Legacy                                      |

| Graphic Controller | 9   | PCI INTA# | Shared with Encryption and Audio Controller |

|                    |     | PCI INTC# |                                             |

| Ethernet           | 10  | PCI INTB# | Do not use with other devices               |

|                    |     | PCI INTC# |                                             |

| Free               | 11  | -         | Available on PC/104 bus                     |

| Mouse              | 12  | -         | Legacy                                      |

| FPU                | 13  | -         | Legacy                                      |

| IDE                | 14  | -         | Primary IDE channel                         |

| Free               | 15  | -         | Available on PC/104 bus                     |

Tab. 4 Hardware Interrupt Table

# 3.7. Peripheral Devices

#### 3.7.1. Scope

The peripheral devices described in this chapter are the core features of the NETSBC-6A board. Meaning that they're available on all the derivates. Special features implemented only on one special board are described in a separate chapter of this documentation.

# 3.7.2. Socket Memory

The NETSBC-6A features a DIL32 socket (P9) for user insertable memory devices like SRAM, NVRAM and EEPROM products. Supported devices and corresponding configuration is listed in the table below, maximum access time allowed is 150 ns for all devices. Note that the Socket Memory base address, size and enabling must also be configured by software (BIOS).

| Memory        | Manufacturer and Order Code | J6 Setting                    | J4 Setting |

|---------------|-----------------------------|-------------------------------|------------|

| Type          |                             | (pins 8, 9,10,12 only)        |            |

| SRAM          | Static RAM (5V)             | 5V, Battery Backup enabled    |            |

| 128k x 8      | Samsung: K6X1008C2D-DB70    | 8-10                          | 2-3        |

|               | Hitachi: HM628128BLP-7      |                               |            |

|               | STMicro: M68AF127BL70B6     |                               |            |

| 512k x 8      | Samsung: K6T4008C1C-DB70    | 8-10                          | 1-2        |

|               | Hitachi: HM628512BLP-7      |                               |            |

|               | Mitsubishi: M5M5408AP-70L   |                               |            |

| NVRAM         | Nonvolatile RAM (5V)        | 5V, Battery Backup disabled   |            |

| 32k x 8       | ZMD: U637256DC70            | 9-10                          | 2-3        |

| 32k x 8       | Simtek: STK16C88-W45        | 9-10                          | 2-3        |

| NVRAM         | Nonvolatile RAM (3.3V)      | 3.3V, Battery Backup disabled |            |

| 128k x 8      | Simtek: STK16CA8-W45        | 10-12                         | 2-3        |

| <b>EEPROM</b> | EEPROM (5V)                 | 5V, Battery Backup disabled   |            |

| 32k x 8       | Atmel: AT28C256(E)-15PC     | 9-10                          | 2-3        |

|               | Catalyst: CAT28C256(H)P-15  |                               |            |

|               | Hitachi: HN58C256AP-10      |                               |            |

|               | ST: M28256-15BS             |                               |            |

|               | Xicor: X28C256P-15          |                               |            |

| 64k x 8       | Catalyst: CAT28C512(H)P-15  | 9-10                          | 2-3        |

|               | SST: SST29EE512A-90-4C-PH   |                               |            |

|               | Xicor: X28C512P-15          |                               |            |

| 128k x 8      | Atmel: AT28C010(E)-15PC     | 9-10                          | 2-3        |

|               | SST: SST29EE010A-120-4C-    |                               |            |

|               | РН                          |                               |            |

|               | Xicor: X28C010D-15          |                               |            |

Tab. 5 Socket Memory Configuration

# **Important Note**

Do not insert devices not listed. This could damage the hardware.

# **Important Note**

For DiskOnChip device support plese contact the manufacturer.

#### **Important Note**

When inserting a 28 pin device into the 32 pin socket, pin 1 of the 28 pin device must be positioned at pin 3 of the DIL32 socket, otherwise the hardware may get damaged.

#### 3.7.3. VGA Interface

The VGA signals are available on the High Density DVI-D connector connector P5 for direct connection of VGA compatible monitors. The controller uses the standard VGA register interface. All configuration is done by software (BIOS, VGA-BIOS).

#### 3.7.4. DVI Interface

The DVI (Digital Visual Interface) signals are available on the High Density DVI-D connector P5 for direct connection of DVI compatible monitors. The signals from the SDVO (Serial Digital Video Out) port are converter into DVI signals from the The controller uses the standard VGA register interface. All configuration is done by software (BIOS, VGA-BIOS).

#### **Device Connection**

| Pin Number | Signal     | Remarks          |

|------------|------------|------------------|

| 1          | DATA#2     |                  |

| 2          | DATA2      |                  |

| 3          | Shield 2/4 | Connected to GND |

| 4          | DATA#4     | Not connected    |

| 5          | DATA4      | Not connected    |

| 6          | DDC_CLK    |                  |

| 7          | DDC_DATA   |                  |

| 8          | VSYNC      | VGA Vertic. Sync |

| 9          | DATA#1     |                  |

| 10         | DATA1      |                  |

| 11         | Shield 1/3 | Connected to GND |

| 12         | DATA#3     | Not connected    |

| 13         | DATA3      | Not connected    |

| 14         | VCC5       | +5Vdc            |

| 15         | GND        |                  |

| 16         | HPDET      | Hot Plug Detect  |

| 17         | DATA#0     |                  |

| 18         | DATA0      |                  |

| 19         | Shield 0/5 | Connected to GND |

| 20         | DATA#5     |                  |

| 21         | DATA5      |                  |

| 22         | Shield CLK | Connected to GND |

| 23         | CLK        |                  |

| 24         | CLK#       |                  |

|            |            |                  |

| C1         | VGA_RED    | VGA Red          |

| C2         | VGA_GREEN  | VGA Green        |

| C3         | VGA_BLUE   | VGA Blue         |

| C4         | HSYNC      | VGA Horiz. Sync  |

| C5         | VGA_GND    |                  |

Tab. 6 DVI-D connector P5

# **Important Note**

Be careful when using the VGA or video signals on expansion boards. Special design and layout precautions must be met for these high speed analog signals.

Maximum cable length allowed for VGA connection is 15 m.

Use high quality VGA cables (with coaxial wires for RGB signals) for maximum EMI protection.

#### 3.7.5. IDE/CompactFlash-Interface

The IDE interface is setup as Primary IDE Channel with standard PC address decoding and using hardware interrupt 14. It supports 2 external devices on a single connection, one configured as master the other as slave. Alternatively one external device may be replaced by an on board pluggable CompactFlash card. The IDE timing is setup by software (BIOS autodetection).

The IDE interface provides the following configuration options:

# **Configuration Options**

| Jumper | Configuration                                    | Remarks            |

|--------|--------------------------------------------------|--------------------|

| J6     | Pin 2-4 open = on board CompactFlash is slave    | don't care if only |

|        | Pin 2-4 closed = on board CompactFlash is master | external devices   |

|        |                                                  | are connected.     |

Tab. 7 IDE Configuration Options

#### **Device Connection**

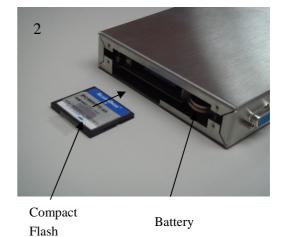

External IDE devices are connected through the standard 2x20 pin header P7. A CompactFlash card may be directly plugged in the on board CompactFlash connector P8.

| Pin Number | Signal  | Pin Number | Signal |

|------------|---------|------------|--------|

| 1          | RST#    | 2          | GND    |

| 3          | HD7     | 4          | HD8    |

| 5          | HD6     | 6          | HD9    |

| 7          | HD5     | 8          | HD10   |

| 9          | HD4     | 10         | HD11   |

| 11         | HD3     | 12         | HD12   |

| 13         | HD2     | 14         | HD13   |

| 15         | HD1     | 16         | HD14   |

| 17         | HD0     | 18         | HD15   |

| 19         | GND     | 20         | NC     |

| 21         | DRQ     | 22         | GND    |

| 23         | HIOW#   | 24         | GND    |

| 25         | HIOR#   | 26         | GND    |

| 27         | IOCHRDY | 28         | GND    |

| 29         | DACK#   | 30         | GND    |

| 31         | IRQ     | 32         | NC     |

| 33         | HA1     | 34         | PDIAG# |

| 35         | HA0     | 36         | HA2    |

| 37         | HCS0#   | 38         | HCS1#  |

| 39         | DASP#   | 40         | GND    |

| 41         | VCC     | 42         | VCC    |

| 43         | GND     | 44         | NC     |

Tab. 8 IDE Connector P7 (2x22 pin)

# **Important Notes**

Do not connect 2 external devices and a CompactFlash card together. This may damage the system and the IDE devices.

#### Note

The NETSBC-6A offers a 5V supply (not fused) for direct plugin IDE/CompactFlash adapters. Max. allowed current drawing is 100mA.

# 3.7.6. Serial Ports 1/2

Two serial ports are available. The serial ports have fixed base addresses of 3F8H for COM1 and 2F8H for COM2. COM1 uses hardware interrupt 4 and COM2 uses hardware interrupt 3.

#### **Device Connection**

The Serial Port COM1 is available on the DSUB9 connector P14A (bottom).

The Serial Port COM2 is available on the DSUB9 connector P15A (bottom).

| Pin Number | Signal | Remarks |

|------------|--------|---------|

| 1          | DCD*   |         |

| 2          | RXD    |         |

| 3          | TXD    |         |

| 4          | DTR*   |         |

| 5          | GND    |         |

| 6          | DSR*   |         |

| 7          | RTS*   |         |

| 8          | CTS*   |         |

| 9          | RI*    |         |

Tab. 9 Serial Ports COM1 and COM2

#### Optional RS485 Interface on COM2 Port

# **Important Note**

This chapter will be added in a future release.

# 3.7.7. USB Interface

The NETSBC-6A features an OHCI/EHCI compatible USB Hostcontroller having assigned the base address and IRQ at boot time by the PCI-BIOS. Four channels are available where as channel 3 can be configured as a device.

#### **Device Connection**

The USB interface uses two dual USB connectors. USB2 and USB3 are also availabe on an internal header (J10).

| P20        | USB channel 0 | P20        | USB channel 1 |

|------------|---------------|------------|---------------|

| (top)      | Signal        | (bottom)   | Signal        |

| Pin Number |               | Pin Number |               |

| 1          | VBUS          | 1          | VBUS          |

| 2          | D-            | 2          | D-            |

| 3          | D+            | 3          | D+            |

| 4          | GND           | 4          | GND           |

Tab. 1 USB Interface Connector P20

| P21        | USB channel 2 | P21        | USB channel 3 |

|------------|---------------|------------|---------------|

| (top)      | Signal        | (bottom)   | Signal        |

| Pin Number |               | Pin Number |               |

| 1          | VBUS          | 1          | VBUS          |

| 2          | D-            | 2          | D-            |

| 3          | D+            | 3          | D+            |

| 4          | GND           | 4          | GND           |

Tab. 2 USB Interface Connector P21

The USB signals for channel 1 and 2 are also available on the internal header J10. A standard USB Flash Drive can be connected to this header.

| J10        | USB channel 2 | P15        | USB channel 1 |

|------------|---------------|------------|---------------|

| Pin Number | Signal        | Pin Number | Signal        |

| 1          | VBUS          | 2          | VBUS          |

| 3          | D-            | 4          | D-            |

| 5          | D+            | 6          | D+            |

| 7          | GND           | 8          | GND           |

| 9          | Not connected | 10         | Not connected |

Tab. 10 USB Interface Connector J10 (2x5pin)

# 3.7.8. PS/2 Keyboard/Mouse Interface

The keyboard signals are only available on an internal header J6. However a MiniDIN (PS/2 connector) can be mounted optionally instead of P21 (USB channels 2 and 3). The controller uses hardware interrupt 1 for the keyboard and hardware interrupt 12 for the mouse. The following configuration options are provided:

**Configuration Options**

| Jumper | Configuration                                 | Remarks        |

|--------|-----------------------------------------------|----------------|

| J6     | Pin 1-3, 2-4 closed = Keyboard signals on P13 | Only if P13 is |

|        | Pin 3-5, 4-6 closed = Mouse signals on P13    | mounted        |

Tab. 11 Keyboard/Mouse Configuration Options

#### **Device Connection**

The standard PS/2 connector P13 is not mounted by default. The PS/2 singles are available on the internal header J6 (2x5 pin). P13 is used (if available) for direct connection of the keyboard or mouse (depending on jumper configuration).

| Pin Number | Signal     | Pin Number | Signal          |

|------------|------------|------------|-----------------|

| 1          | KBDATA     | 2          | KBCLK           |

| 3          | P3-1       | 4          | P3-5            |

| 5          | MDATA      | 6          | MCLK            |

| 7          | BM1 / P3-2 | 8          | BM0 / P3-6      |

| 9          | GND        | 10         | +5V (not fused) |

Tab. 12 Keyboard/Mouse internal Header J6 (2x5 pin)

#### **Important Note**

Do not connect the Boot Mode Pins on P3 or P4. These signals may only be used by the Boot Loader Key to start the Boot Loader.

The Boot Loader Key (BOOTPLUG) shortens Pin 3 and 6 of P13.

# **Important Note**

Maximum cable length allowed for keyboard and mouse connection is 3 m. Use shielded cables for maximum EMI protection.

#### 3.7.9. Ethernet Interfaces

The NETSBC-6A features two PCI Ethernet 10/100 baseT controller having assigned the base address and IRQ at boot time by the BIOS. There are two LED's (yellow and green) integrated into the RJ45 connector. The green LED indicates speed. The LED will be on at 100Mbps and off at 10Mbps. The yellow" activity" LED indicates either transmit or receive activity. When activity is present, the LED is on; when no activity is present, the LED is off.

No configuration options are available for the ethernet device.

#### **Device Connection**

The Ethernet interface uses the standard RJ45 connector P18 and P19 for  $100\Omega$  shielded or unshielded Twisted Pair cabling.

| Pin Number | Signal           | Remarks |

|------------|------------------|---------|

| 1          | TX+              |         |

| 2          | TX-              |         |

| 3          | RX+              |         |

| 4-5        | line termination |         |

| 6          | RX-              |         |

| 7-8        | line termination |         |

Tab. 13 Ethernet Twisted Pair Interface Connector P18 and P19 (RJ45)

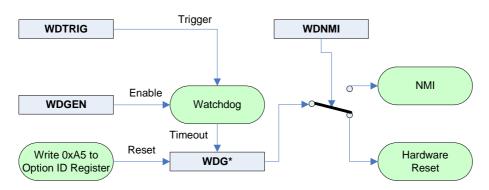

### 3.7.10. Watchdog

The watchdog timer is configurable for 100 ms or 1.6 s timeout. Once timed out, it may activate the NETSBC-6A's hardware.

# **Configuration Options**

| Jumper | Configuration           | Remarks |

|--------|-------------------------|---------|

| J6     | Pin 4-6 open = 1.6 s    |         |

|        | Pin 4-6 closed = 100 ms |         |

Tab. 14 Watchdog Configuration Options

### 3.7.11. Power Supply

The processor and its peripherals are powered by a non-isolated, integrated power supply which generates all the necessary voltages.

See paragraph 6.2 for connection details.

# **Configuration Options**

| Switch  | Configuration                            | Remarks |

|---------|------------------------------------------|---------|

| S12:1/2 | on/off = external power on/off input pin | P1:3    |

|         | off/on = external power fail input pin   |         |

Tab. 15 Power Supervision Configuration Options

In some application it can be useful when the digital ground plane (GND) is connected to shield. In order to short circuit the two power planes two jumpers have to be placed on J16.

| Jumper | Configuration                             | Remarks |

|--------|-------------------------------------------|---------|

| J100   | Pin 1-2 closed = shield and GND connected |         |

|        | Pin 3-4 closed = shield and GND connected |         |

Tab. 16 Power plane short circuit

#### 3.7.12. Power supervision

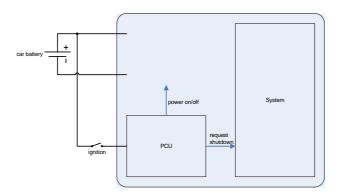

This feature is implemented on systems with #3 or higher.

The power management control unit (PCU) contains of RISC microcontroller and is implemented on the base board.

The PCU can be operated in two modes: power fail mode or remote on/off mode.

The following two chapters describe their functionality in detail.

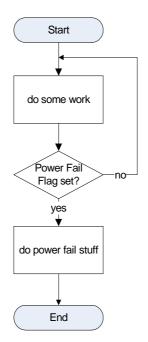

#### 3.7.13. Power Fail

In power fail mode the microcontroller monitors the external power fail signal. The state of power fail signal can be access through the status register, I/O 8200h.

# **Application example**

Fig. 7 Typical power fail application

The application has to poll the power fail flag and call different functions according to the state of the flag.

Fig. 8 Typical power fail flow

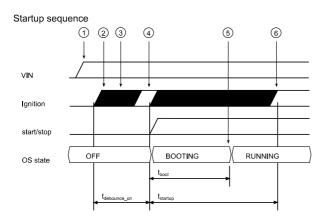

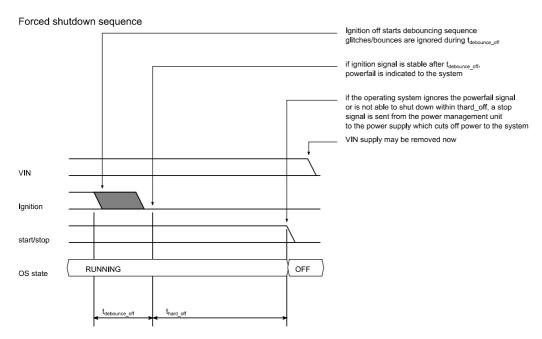

# 3.7.14. Remote On/Off

With the remote on/off function the system can be switched on and of through an external control signal. When active the internal software goes from the run state into the shutdown state. After a predefined timeout the PCU switches the main power supply off. The timeout can be configured through S14.

| Config switch position | t <sub>debounce_on</sub><br>On debouncing<br>(setup) | t <sub>debounce_off</sub><br>Off debouncing<br>(hold) | t <sub>startup</sub> Hold time until switch off signal is routed to processor, if system is still booting | t <sub>hard_off</sub> Timeout until switch off signal is generated from processor (after that hard off) |

|------------------------|------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 0                      | -                                                    | -                                                     | -                                                                                                         | -                                                                                                       |

| 1                      | 2 s                                                  | 60 s                                                  | 5 s                                                                                                       | 1 min                                                                                                   |

| 2                      | 2 s                                                  | 60 s                                                  | 60 s                                                                                                      | 5 min                                                                                                   |

| 3                      | 2 s                                                  | 60 s                                                  | 30 min                                                                                                    | 2 h                                                                                                     |

| 4                      | 2 s                                                  | 60 s                                                  | 2 h                                                                                                       | 2 h                                                                                                     |

| 5 – F                  | N/a                                                  | n/a                                                   | n/a                                                                                                       | n/a                                                                                                     |

Tab. 17 PCU timing configuration through S14

When switch S14 is in position 0 the PCU is in bypass mode.

# **Application example**

Fig. 9 Application example: CAR PC

Fig. 10 Startup timing diagram

#### Notes

- 1) VIN supply must be present

- 2) Ignition on starts debouncing sequence

- 3) glitches/bounces are ignored during  $\rm t_{debounce\_on}$

- 4) if ignition signal is stable after  $t_{\tt debounce\_on}$  supply is switched on and the system starts

- 5) during t<sub>startup</sub>, ignition switch is ignored Note: system might have finished booting well in advance before startup phase is over

- 6) after  $t_{\mbox{\tiny startup}},$  the power management circuit resumes tracking of the ignition switch signal

Fig. 11 Shutdown timing diagram

#### **Important Notes**

The operating system must support the remote on/off function.

#### **Power Fail**

A power fail can occur on two occasions: the external ipnut is pulled low or the power supply voltage drops below approx. 8.9Vdc.

| Connector | Configuration                                    | Remarks          |

|-----------|--------------------------------------------------|------------------|

| P1:3      | voltage > 2.5Vdc or left open = normal operation | S12:1/2 = off/on |

|           | voltage < 2.5Vdc = power fail                    |                  |

| P1:1-2    | voltage >= 9.0Vdc = normal operation             | S12:1/2 = off/on |

|           | voltage < 8.9Vdc = power fail                    |                  |

Tab. 18 Power Fail

#### Remote On/Off

In some applications it is desirable that when a under-voltage event occurs that the systems shuts down.

| Connector | Configuration                            | Remarks          |

|-----------|------------------------------------------|------------------|

| P1:3      | voltage > 2.5Vdc = normal operation      | S12:1/2 = on/off |

|           | voltage < 2.5Vdc or left open = shutdown |                  |

| P1:1-2    | voltage >= 9.0Vdc = normal operation     | S12:1/2 = on/off |

|           | voltage < 8.9Vdc = shutdown              |                  |

Tab. 19 Remote On/Off

#### **Important Note**

The functions mentioned above are only available in systems with revision 3 or higher

#### 3.7.15. Configurations Switches

There are two rotary Hex-Switches for customer use available, where only S1 can be accessed by removing the left side cover. The values can be read from a register at I/O address 820Ch

#### 3.7.16. Factory Programming Header

The programmable logic devices on the NETSBC-6A board are factory programmed using some pins of the internal header J5. These pins **must not** be connected by the user.

| Pin Number | Signal | Remarks    |

|------------|--------|------------|

| 1          | TCK    | do not use |

| 3          | TDO    | do not use |

| 5          | TMS    | do not use |

| 7          | TDI    | do not use |

Tab. 20 Factory Programming Header J5 (2x5 pin)

#### 3.7.17. LPC Header

The internal LPC (Low Pin Count) bus is available on the header J3. These pins **must not** be connected by the user.

| Pin Number | Signal | Remarks    |

|------------|--------|------------|

| 1          | AD0    | do not use |

| 2          | AD1    | do not use |

| 3          | AD2    | do not use |

| 4          | AD3    | do not use |

| 5          | FRAME# | do not use |

| 6          | RST#   | do not use |

| 7          | CLK    | do not use |

Tab. 21 LPC J3 (1x7 pin)

#### 3.7.18. Isolated Power Supply

Instead of the synchronous buck controller a DC/DC converter can be soldered onto the board for isolating the power supply. The input range will be reduced. For further information please contact the manufacturer

#### 3.8. Optional Functions

There are several functions on the NETSBC-6A which aren't implemented on the standard Syslogic product:

- isolated power supply

- parallel port

- RS485 interface at COM2

- up to two isolated CAN interfaces

- 24bit LVDS (6bit/8bit) including brightness control

- AC97 audio port

For further technical information and customization details please contact Syslogic sales.

#### 3.9. Hardware Limitations

#### 3.9.1. PCI Bus Limitations

- Only 3.3V PCI bus

- PCI bus speed is limited to 33MHz

#### 3.9.2. ISA Bus Limitations

- The interrupt lines are pulled up with 8k2 resistors to Vcc (EISA specification) instead of 2k2 (IEEE 996)

- NMI (IOCHCK#) is not supported on the PC/104

- Only a predefined amount of I/O addresses are available on the PC/104 bus, please refer to the appropriate chapter for details

# **4 Programming Information**

#### 4.1. Overview

The programming of the NETSBC-6A board is done with standard memory and I/O read and write operations. Most configuration options are handled by the BIOS. For detailled information refer to the NETSBC-6A firmware documentation and other related documents as listed in paragraph 1.4.

## 4.2. Interrupt, Memory and I/O Resources

#### 4.2.1. Interrupt Resources

Please refer to chapter 3.6 for the table showing the usage of the NETSBC-6A's interrupts.

#### 4.2.2. Memory Resources

The general memory layout is shown in paragraph 3.2.1. The configuration of the memory layout is done by programming Geode internal configuration registers and board configuration registers (see paragraph 4.2.3). This is done completely by the BIOS on system startup and must not be changed during operation. For operating systems requiring memory configuration (e.g. Windows CE) the memory layout shown in paragraph 3.2.1 must be considered.

#### 4.2.3. I/O Resources

This paragraph describes only the NETSBC-6A system register and support functions not directly related to a specific peripheral device. The general I/O layout is shown in paragraph 3.2.2. Peripheral devices are discussed in paragraph 0. Note that the Socket Memory related registers are programmed by the BIOS on system startup and must not be changed during operation except for the Socket Memory Window Mapping Register in case of user controlled memory mapping (allowing access to 512kbyte Socket Memory as eight 64kbyte blocks in the Socket Memory window below 1M in Real Mode).

| Address   | Device / Register                          | Remarks           |

|-----------|--------------------------------------------|-------------------|

| 8200h     | Status Register                            |                   |

| 8201h     | Control Register                           | Reset state = 05H |

| 8202h     | Function ID Register                       |                   |

| 8203h     | reserved                                   | do not write      |

| 8204h     | Option ID Register                         |                   |

| 8205h     | Setup Register                             | Reset state = 00H |

| 8206h     | Revision ID Register                       |                   |

| 8207h     | Socket Memory Configuration Register       | Reset state = 00H |

| 8208h     | Socket Memory Window Mapping Register      | Reset state = 00H |

| 8209h     | Socket Memory Window Base Address Register | Reset state = D0H |

| 820Ah     | Boot Mode Input Register                   |                   |

| 820Bh     | I2C Register                               | for Temp Sensor   |

| 820Ch     | Switch Register                            | do not write      |

| 820Dh     | reserved                                   | do not access     |

| 820F821Fh | reserved                                   | do not access     |

Tab. 22 NETSBC-6A System Registers

#### **Status Register**

Reading I/O Register 8200h:

| D7       | D6     | D5 | D4   | D3       | D2       | D1      | D0  |

|----------|--------|----|------|----------|----------|---------|-----|

| OVERTMP* | LOBAT* | 1  | WDG* | ERRFLAG* | ATTFLAG* | ERRINT* | PF* |

#### Description:

- PF\*: Power Fail Status

0 = Power Fail occurred1 = normal operation

- ERRINT\*: Error Interrupt Status

0 = Error Interrupt pending on this module

1 = no Error Interrupt pending on this module

- ATTFLAG\*: Attention Status Flag (for polled applications)

not used, returns 1

- ERRFLAG\*: Error Status Flag (for polled applications)

not used, returns 1

- WDG\*: Watchdog Status Flag

0 = Watchdog has timed out

1 = Watchdog running or disabled

Reset by issuing a hardware reset (see register 8204H)

- LOBAT\*: Battery Status Flag

0 = Battery voltage low

$1 = Battery \ voltage \ ok$

- OVERTMP\*: Temperatur Sensor Status Flag

0 = programmed temperatur limit reached

1 = temperatur ok (below limit)

#### Writing I/O Register 8200h:

| *************************************** |          |          |          |          |          |          |          |

|-----------------------------------------|----------|----------|----------|----------|----------|----------|----------|

| D7                                      | D6       | D5       | D4       | D3       | D2       | D1       | D0       |

| reserved                                | reserved | reserved | reserved | reserved | reserved | reserved | reserved |

#### Description:

- reserved: reserved, always write 0

#### **Control Register**

Reading I/O Register 8201h:

| D7      | D6     | D5    | D4   | D3      | D2     | D1     | D0     |

|---------|--------|-------|------|---------|--------|--------|--------|

| TRIGGER | WDTRIG | WDNMI | STOP | TRIGSRC | FREEZE | ERREN* | ATTEN* |

#### Description:

- ATTEN\*: Attention Interrupt Enable

not used, returns 1

- ERREN\*: Error Interrupt Enable (IOCHCK\* routed to NMI)

0 = Error interrupt on NMI enabled (always enabled)

- FREEZE: not used, returns 1

- TRIGSRC: NETIPC TRIGGER\* Signal Source Select

always 1

- STOP: NETIPC STOP\* Signal State

0 = STOP\* inactive (high)

1 = STOP\* active (low)

- WDNMI: Watchdog action Select

0 = Watchdog timeout activates hardware reset

1 = not supported

- WDTRIG: Watchdog Trigger

any state change triggers the watchdog (timeout reset)

- TRIGGER: Direct Control for NETIPC TRIGGER\* Signal always 1

#### Writing I/O Register 8201h:

| D7      | D6     | D5    | D4   | D3      | D2     | D1     | D0     |

|---------|--------|-------|------|---------|--------|--------|--------|

| TRIGGER | WDTRIG | WDNMI | STOP | TRIGSRC | FREEZE | ERREN* | ATTEN* |

#### Description:

- ATTEN\*: Attention Interrupt Enable

not used

- ERREN\*: Error Interrupt Enable (IOCHCK\* routing to NMI)

0 = enable Error interrupt on NMI (always enabled)

- FREEZE: not used

- TRIGSRC: NETIPC TRIGGER\* Signal Source Select

always write 1

- STOP: NETIPC STOP\* Signal State

0 = STOP\* inactive (high)

1 = STOP\* active (low)

- WDNMI: Watchdog action Select

always write 0

- WDTRIG: Watchdog Trigger

any state change triggers the watchdog (timeout reset)

TRIGGER: Direct Control for NETIPC TRIGGER\* Signal (if enabled by TRIGSRC bit in Control Register) always write 1

The Trigger feature is not supported on the IPC/NETIPC-6 boards.

| TRIGSRC | TRIGGER | TRIGGER* Source                                                        |

|---------|---------|------------------------------------------------------------------------|

| 0       | 0       | Square Wave Output (SQW) of Real Time Clock Device                     |

| 0       | 1       | Timer (8254) Channel 2 Output gated with Port B bit 1 (Speaker Enable) |

| 1       | X       | TRIGGER bit directly controls the TRIGGER* output                      |

#### Tab. 23 TRIGGER\* Source Selection

## **Function ID Register**

#### Reading I/O Register 8202h:

| Γ | D.7                   | D.   | D.   | D 4  | D.0  | DA   | D.1  | <b>D</b> 0 |

|---|-----------------------|------|------|------|------|------|------|------------|

|   | $\mathbf{D}^{\prime}$ | D6   | D5   | D4   | D3   | D2   | DI   | D0         |

|   | FID7                  | FID6 | FID5 | FID4 | FID3 | FID2 | FID1 | FID0       |

#### Description:

- FID7..0: Function ID

0101'0001 (51h) = general NETIPC board, subtype defined by Option ID Register

## Writing I/O Register 8202h:

| D7       | D6       | D5       | D4       | D3       | D2       | D1       | D0       |

|----------|----------|----------|----------|----------|----------|----------|----------|

| reserved |

#### Description:

- reserved: reserved, always write 0

#### **Option ID Register**

#### Reading I/O Register 8204h:

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|

| OPT7 | OPT6 | OPT5 | OPT4 | OPT3 | OPT2 | OPT1 | OPT0 |

#### Description:

- OPT7..0: Option ID

1011'1000 (B8h) = IPC/NETSBC-6, 512MB (if FID = 51h)

#### Writing I/O Register 8204h:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|----|----|----|----|----|----|----|----|

| X  | X  | X  | X  | X  | X  | X  | X  |

#### Description:

xxxxxxxx: Writing data A5h invokes a complete hardware reset (also clearing the Watchdog timeout status bit)

## **Setup Register**

#### Reading I/O Register 8205h:

| D7    | D6   | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|------|----|----|----|----|----|----|

| READY | WDEN | 0  | 0  | 0  | 0  | 0  | 0  |

#### Description:

- WDEN: Watchdog Enable

0 = Watchdog disabled

1 = Watchdog enabled (running)

- READY: NETIPC READY Signal State

0 = READY inactive 1 = READY active

#### Writing I/O Register 8205h:

| D7    | D6   | D5       | D4       | D3       | D2       | D1       | D0       |

|-------|------|----------|----------|----------|----------|----------|----------|

| READY | WDEN | reserved | reserved | reserved | reserved | reserved | reserved |

#### Description:

- reserved: reserved, always write 0

- WDEN: Watchdog Enable

0 = Watchdog disabled (cannot be disabled while running)