user documentation

# IPC/ML71xxx-xxxE

Document Ordercode: DOC/COMPACT71-MLE

| Revision | Date       | Author      | Modification                                                              |  |

|----------|------------|-------------|---------------------------------------------------------------------------|--|

| 0.1      | 18.01.2013 | R. Newbould | Preliminary release                                                       |  |

| 0.2      | 15.02.2013 | F. Liechti  | Reworked Power Fail                                                       |  |

| 1.0      | 16.05.2013 | R. Newbould | Release Version                                                           |  |

| 1.1      | 10.10.2013 | R. Newbould | New revisions added, temperature range corrected                          |  |

| 1.2      | 23.12.2013 | R. Newbould | Bat. life time, safety and power supply added, IPC/BL71-107E, -109E added |  |

| 1.3      | 06.09.2014 | F. Liechti  | Power management description modified                                     |  |

# Contents

| 1 | Intro | duction    |                                   | 9  |

|---|-------|------------|-----------------------------------|----|

|   | 1.1.  | General    | remarks                           | 9  |

|   | 1.2.  | Contents   | s of this documentation           | 9  |

|   | 1.3.  | Naming     | conventions                       | 9  |

|   | 1.4.  | -          | nal products and documents        | 9  |

|   |       | 1.4.1.     | Software products                 | 9  |

|   | 1.5.  | Docume     | ents and references               | 9  |

|   |       | 1.5.1.     | Syslogic documentation            | 9  |

|   |       | 1.5.2.     | Standards and books               | 9  |

|   |       | 1.5.3.     | Datasheets                        | 10 |

|   | 1.6.  | ltems de   | elivered                          | 10 |

|   | 1.7.  | Safety re  | ecommendations and warnings       | 10 |

|   |       | 1.7.1.     | EMC                               | 11 |

|   |       | 1.7.1.     | Battery                           | 12 |

|   |       | 1.7.2.     | Hot surface                       | 12 |

|   | 1.8.  | Electro-s  | static discharge                  | 12 |

|   | 1.9.  | Life cycle | e information                     | 12 |

|   |       | 1.9.1.     | Transportation and storage        | 12 |

|   |       | 1.9.2.     | Operation                         | 12 |

|   |       | 1.9.3.     | Maintenance and repair            | 12 |

|   |       | 1.9.4.     | Warranty                          | 13 |

|   |       | 1.9.5.     | RoHS                              | 13 |

|   |       | 1.9.6.     | Disposal and WEEE                 | 13 |

| 2 | Prod  | uct desci  | ription                           | 14 |

|   | 2.1.  |            | -<br>71 Systems                   | 14 |

|   | 2.2.  | Features   |                                   | 14 |

|   |       | 2.2.1.     | CPU core                          | 14 |

|   |       | 2.2.2.     | Memory                            | 14 |

|   |       | 2.2.3.     | Graphics controller               | 14 |

|   |       | 2.2.4.     | CFast and SATA interface          | 14 |

|   |       | 2.2.5.     | Integrated peripherals            | 15 |

|   |       | 2.2.6.     | PS/2 mouse and keyboard interface | 15 |

|   |       | 2.2.7.     | Serial ports                      | 15 |

|   |       | 2.2.8.     | Universal serial bus              | 15 |

|   |       | 2.2.9.     | Ethernet                          | 15 |

|   |       | 2.2.10.    | Firmware flash memory             | 15 |

|   |       | 2.2.11.    | Real time clock                   | 15 |

|   |       | 2.2.12.    | Configuration switches            | 15 |

|   |       | 2.2.13.    | SPI                               | 15 |

|   |       | 2.2.14.    | SMBus (I2C)                       | 15 |

|   |       | 2.2.15.    | HDA/SPKR                          | 15 |

|   |      | 2.2.16.            | LPC                                                    | 16       |

|---|------|--------------------|--------------------------------------------------------|----------|

|   |      | 2.2.17.            | Power Supply                                           | 16       |

|   |      | 2.2.18.            | PC/104 Bus Interface                                   | 16       |

|   |      | 2.2.19.            | CAN Interface                                          | 16       |

|   | 2.3. | Product            | Variants                                               | 18       |

| 3 | Hard | ware des           | scription                                              | 19       |

|   | 3.1. | Overview           | W                                                      | 19       |

|   | 3.2. | Memory             | / and I/O resources                                    | 25       |

|   |      | 3.2.1.             | General memory layout and configuration                | 25       |

|   |      | 3.2.2.             | General I/O Layout and configuration                   | 26       |

|   | 3.3. | Intel Ato          | om E6xxT Processor                                     | 28       |

|   | 3.4. |                    | e devices                                              | 29       |

|   | 3.5. |                    | tform Controller Hub EG20T                             | 30       |

|   | 3.6. |                    | re interrupts                                          | 31       |

|   | 3.7. | DMA cha            |                                                        | 32       |

|   | 3.8. |                    | ral devices                                            | 32       |

|   |      | 3.8.1.             | Scope                                                  | 32       |

|   |      | 3.8.2.             | DVI interface                                          | 32       |

|   |      | 3.8.3.             | LVDS                                                   | 33       |

|   |      | 3.8.4.             | SATA/CFast-interface                                   | 36       |

|   |      | 3.8.5.             | Serial port 1 (RS232)                                  | 38       |

|   |      | 3.8.6.             | Serial port 2 (RS232)                                  | 38       |

|   |      | 3.8.7.             | Serial port 3 (RS232)                                  | 39       |

|   |      | 3.8.8.             | Serial port 4 (RS232)                                  | 40       |

|   |      | 3.8.9.             | Serial port 4 (RS485)                                  | 40       |

|   |      | 3.8.10.            | Serial port 5 (RS232)                                  | 41       |

|   |      | 3.8.11.            | Serial port 5 (RS485)                                  | 41       |

|   |      | 3.8.12.            | Serial port 6 (RS232)                                  | 43       |

|   |      | 3.8.13.            | Serial port 6 (RS485)                                  | 43       |

|   |      | 3.8.14.            | USB interface                                          | 44       |

|   |      | 3.8.15.            | USB Device                                             | 46       |

|   |      | 3.8.16.            | Ethernet interfaces                                    | 46       |

|   |      | 3.8.17.            | RGMII<br>Sustan Management Bug (12C)                   | 46       |

|   |      | 3.8.18.            | System Management Bus (I2C)                            | 47       |

|   |      | 3.8.19.<br>7.0.20  | Serial Peripheral Interface                            | 48       |

|   |      | 3.8.20.            | High Definition Audio<br>PS/2 Keyboard/Mouse interface | 49<br>49 |

|   |      | 3.8.21.<br>3.8.22. | JTAG                                                   | 49<br>50 |

|   |      |                    | LPC                                                    |          |

|   |      | 3.8.23.<br>3.8.24. | Rotary Switch                                          | 51<br>51 |

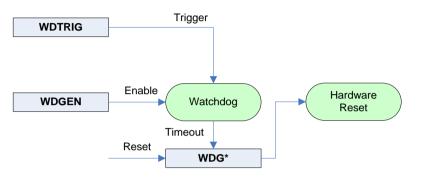

|   |      | 3.8.24.<br>3.8.25. | Watchdog                                               | 51       |

|   |      | 3.8.25.<br>3.8.26. | PC/104 Bus Interface                                   | 52       |

|   |      | 3.8.26.<br>3.8.27. | Power supply                                           | 52       |

|   |      |                    | Backup-Battery                                         | 54       |

|   |      | 3.8.28.            | טמנגעף-טמוופו א                                        | 55       |

|       | 3.8.29.  | Isolated power supply        | 55 |

|-------|----------|------------------------------|----|

|       | 3.8.30.  | Power supervision            | 55 |

|       | 3.8.31.  | Power Fail                   | 55 |

|       | 3.8.32.  | Remote On/Off                | 56 |

|       | 3.8.33.  | CAN interface                | 58 |

| 3.9.  | Hardwa   | re limitations               | 60 |

|       | 3.9.1.   | Peripheral limitations       | 60 |

|       | 3.9.2.   | ISA bus limitations          | 60 |

| Prog  | ramming  | g information                | 61 |

| 4.1.  | Overvie  | W                            | 61 |

| 4.2.  | Interrup | ot, memory and I/O resources | 61 |

|       | 4.2.1.   | Interrupt resources          | 61 |

|       | 4.2.2.   | Memory resources             | 61 |

|       | 4.2.3.   | I/O resources                | 61 |

| 4.3.  | Periphe  | ral devices                  | 72 |

|       | 4.3.1.   | Serial ports                 | 72 |

|       | 4.3.2.   | Keyboard/Mouse interface     | 72 |

|       | 4.3.3.   | Ethernet interfaces          | 72 |

|       | 4.3.4.   | Temperature sensor           | 72 |

|       | 4.3.5.   | Watchdog                     | 72 |

|       | 4.3.6.   | CAN interface                | 73 |

|       |          | ssembly and mounting         | 74 |

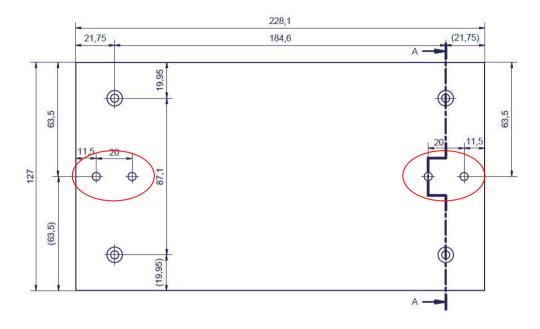

| 5.1.  | -        | 71 dimensions                | 74 |

| 5.2.  | Mountir  | ng options                   | 74 |

| Insta |          | and cabling                  | 76 |

| 6.1.  | Introduo |                              | 76 |

| 6.2.  |          | ng the IPC/ML71 System       | 76 |

|       | 6.2.1.   | General information          | 76 |

|       | 6.2.2.   | Power supply                 | 76 |

|       | 6.2.3.   | Power connection             | 77 |

| 6.3.  |          | the interfaces               | 78 |

|       | 6.3.1.   | Connector locations          | 78 |

|       | 6.3.2.   | IPC/ML71F16-A101E            | 79 |

|       | 6.3.3.   | IPC/ML71F16-A102E            | 80 |

|       | 6.3.1.   | Cable length                 | 81 |

| 6.4.  |          | able Parts                   | 81 |

|       | 6.4.1.   | General information          | 81 |

|       | 6.4.2.   | CFast                        | 82 |

|       | 6.4.3.   | Battery                      | 82 |

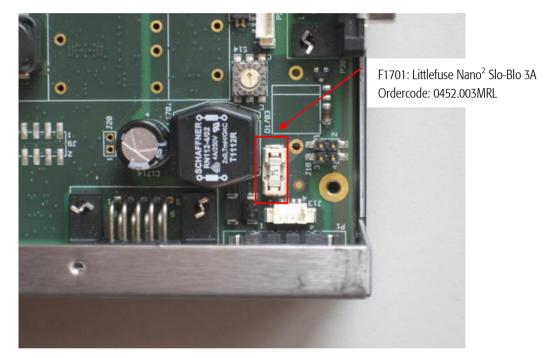

|       | 6.4.4.   | Fuse F1701                   | 83 |

| 7  | Tech  | nical da | Ita                   | 84 |

|----|-------|----------|-----------------------|----|

|    | 7.1.  | Electric | al data               | 84 |

|    | 7.2.  | EMI / E  | MC specification      | 87 |

|    |       | 7.2.1.   |                       | 87 |

|    |       | 7.2.2.   | Emission              | 88 |

|    |       | 7.2.3.   | Immunity              | 89 |

|    | 7.3.  | Enviror  | nmental specification | 89 |

|    | 7.4.  | Mechai   | nical data            | 89 |

| 8  | Firm  | ware     |                       | 90 |

|    | 8.1.  | BIOS     |                       | 90 |

|    |       | 8.1.1.   | General information   | 90 |

|    |       | 8.1.2.   | Main menu             | 90 |

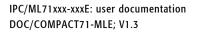

|    |       | 8.1.3.   | Advanced              | 91 |

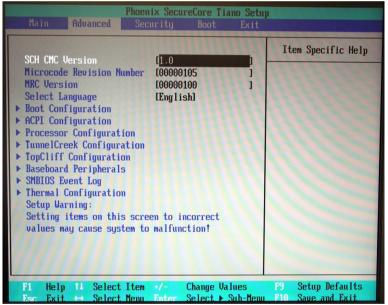

|    |       | 8.1.4.   | Security              | 93 |

|    |       | 8.1.5.   | Boot                  | 94 |

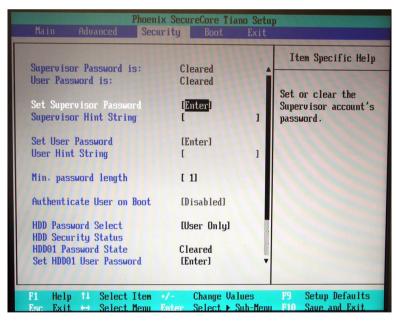

|    |       | 8.1.6.   | Exit                  | 94 |

|    | 8.2.  | BIOS re  | ecovery               | 94 |

| 9  | Oper  | ating sy | ystems                | 96 |

| 10 | Prod  | uct revi | ision history         | 97 |

|    | 10.1. | Hardwa   | are                   | 97 |

|    | 10.2. | Firmwa   | are/BIOS              | 98 |

| 11 | Manu  | ıfacture | er information        | 99 |

|    | 11.1. | Contac   | t                     | 99 |

# List of Tables

| Tab. 1  | Feature List                                      | 18 |

|---------|---------------------------------------------------|----|

| Tab. 2  | List of connectors                                | 22 |

| Tab. 3  | List of headers                                   | 23 |

| Tab. 4  | List of switches                                  | 24 |

| Tab. 5  | Physical Memory Address Space Layout for IPC/ML71 | 25 |

| Tab. 6  | I/O address space layout                          | 28 |

| Tab. 7  | PCI devices EG20T                                 | 31 |

| Tab. 8  | Hardware interrupt table                          | 31 |

| Tab. 9  | DMA channels                                      | 32 |

| Tab. 10 | DVI-D connector P5                                | 33 |

| Tab. 11 | DDC programming header J18                        | 33 |

| Tab. 12 | LVDS connector P3                                 | 34 |

| Tab. 13 | Backlight connector P24                           | 34 |

| Tab. 14 | LDDC programming header P4                        | 34 |

| Tab. 15 | Brightness configuration                          | 35 |

|         |                                                   |    |

| Tab. 16 | LVDS configuration                                                | 35 |

|---------|-------------------------------------------------------------------|----|

| Tab. 17 | CFast Connector P27(SATA Channel 0)                               | 36 |

| Tab. 18 | SATA Data Connector P8 (SATA Channel 1)                           | 37 |

| Tab. 19 | SATA Power Connector P9                                           | 37 |

| Tab. 20 | SATA Connector P26 (SATA Channel 1)                               | 37 |

| Tab. 21 | Serial Port COM1 on DSUB9 P14                                     | 38 |

| Tab. 22 | Serial port COM2 on J7                                            | 38 |

| Tab. 23 | Serial Port COM2                                                  | 39 |

| Tab. 24 | Serial port COM3 on J8                                            | 39 |

| Tab. 25 | Serial port COM4 on J9                                            | 40 |

| Tab. 26 | Serial port COM4 (RS485) on J9                                    | 40 |

| Tab. 27 | RS485 configuration options                                       | 41 |

| Tab. 28 | Serial port COM5 on J10                                           | 41 |

| Tab. 29 | Serial port COM5 (half duplex, RS485) on P30                      | 42 |

| Tab. 30 | Serial port COM5 (full duplex, RS485) on P30                      | 42 |

| Tab. 31 | RS485 configuration options                                       | 42 |

| Tab. 32 | Serial port COM6 on J11                                           | 43 |

| Tab. 33 | Serial port COM 6(half duplex, RS485) on P31                      | 43 |

| Tab. 34 | Serial port COM6 (full duplex, RS485) on P31                      | 44 |

| Tab. 35 | RS485 configuration options                                       | 44 |

| Tab. 36 | USB ports 0 and 1 on P20                                          | 45 |

| Tab. 37 | USB ports 2 and 3 on P21                                          | 45 |

| Tab. 38 | USB ports 4 and 5 on P15 and P16                                  | 45 |

| Tab. 39 | USB device P22 (on bottom side of the PCB)                        | 46 |

| Tab. 40 | Ethernet twisted pair interface connector P17, P18 and P19 (RJ45) | 46 |

| Tab. 41 | RGMII P32                                                         | 47 |

| Tab. 42 | SMBus connected slaves                                            | 47 |

| Tab. 43 | SMB/I2C P6                                                        | 48 |

| Tab. 44 | SPI P33                                                           | 48 |

| Tab. 45 | HDA P23                                                           | 49 |

| Tab. 46 | Speaker P7                                                        | 49 |

| Tab. 47 | Keyboard/Mouse internal header J6 (2x5 pin)                       | 50 |

| Tab. 48 | Keyboard/Mouse configuration options                              | 50 |

| Tab. 49 | JTAG interface header J4                                          | 50 |

| Tab. 50 | LPC interface header J3                                           | 51 |

| Tab. 51 | Watchdog configuration options                                    | 51 |

| Tab. 52 | PC/104 bus connectors PA/PB, PC/PD                                | 52 |

| Tab. 53 | External Battery Connector P11 (1x6 pin)                          | 53 |

| Tab. 54 | User Programmable Output Connector P12 (1x6 pin)                  | 53 |

| Tab. 55 | Power supply connector P1 (1x4 pin)                               | 54 |

| Tab. 56 | Power supply header J13 (1x4 pin)                                 | 54 |

| Tab. 57 | Power supply configuration                                        | 54 |

| Tab. 58 | Power plane short circuit                                         | 54 |

| Tab. 59 | Backup-Battery on header P29 (1x2 pin)                            | 55 |

| Tab. 60 | PCU timing configuration through S14                              | 57 |

|         |                                                                   |    |

| Tab. 61 | Pin assignment of CAN interface: CAN1 at P30 / CAN2 at P31 | 59 |

|---------|------------------------------------------------------------|----|

| Tab. 62 | CAN interfaces 1 and 2 on J21 and J22                      | 59 |

| Tab. 63 | Terminatino resistor                                       | 59 |

| Tab. 64 | Termination resistor                                       | 60 |

| Tab. 65 | IPC/ML71 and IPC/SL71 System Registers                     | 61 |

| Tab. 66 | IPC/ML71 and IPC/SL71 CAN Specific System Registers        | 62 |

| Tab. 67 | I2C Address Space                                          | 72 |

| Tab. 68 | Power connector pinout                                     | 77 |

| Tab. 69 | Weidmüller power connector                                 | 77 |

| Tab. 70 | IPC/ML71F16-A101E: Connectors                              | 79 |

| Tab. 71 | IPC/ML71F16-A102E: Connectors                              | 80 |

| Tab. 72 | Maximum cable length of all interfaces                     | 81 |

| Tab. 73 | General absolute maximum ratings                           | 84 |

| Tab. 74 | General recommended operating conditions                   | 85 |

| Tab. 75 | General electrical characteristics                         | 86 |

| Tab. 76 | General switching characteristics                          | 87 |

| Tab. 77 | Emission requirements                                      | 88 |

| Tab. 78 | Immunity requirements                                      | 89 |

| Tab. 79 | Hardware revision state                                    | 97 |

| Tab. 80 | BIOS revision state                                        | 98 |

# List of Figures

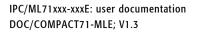

| Fig. 1 Block   | diagram (IPC/ML71)                                                         | 17 |

|----------------|----------------------------------------------------------------------------|----|

| Fig. 2 Board   | l layout (IPC/BL71)                                                        | 20 |

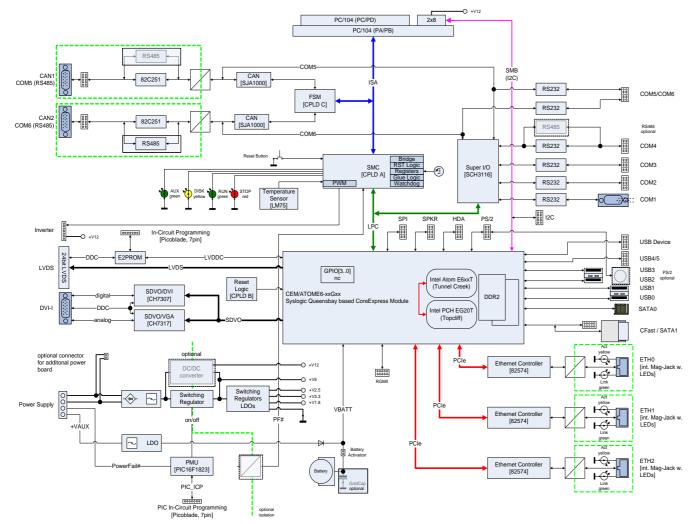

| Fig. 3 Memo    | pry map                                                                    | 26 |

| Fig. 4 Intel A | Atom Processor E6xx                                                        | 29 |

| Fig. 5 PCI Ex  | xpress Subsystem                                                           | 29 |

| Fig. 6 Intel P | Platform Controller Hub EG20T                                              | 30 |

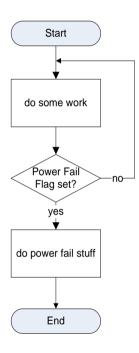

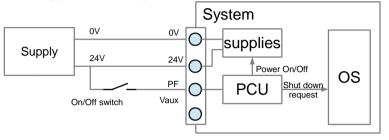

| Fig. 7         | Typical power fail application                                             | 56 |

| Fig. 8         | Typical power fail flow                                                    | 56 |

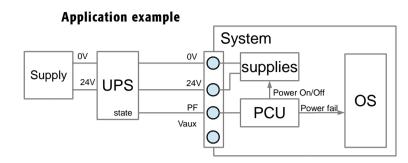

| Fig. 9         | Application example: Remote On/Off                                         | 57 |

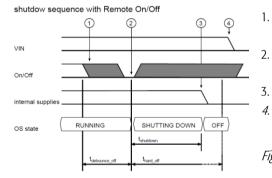

| Fig. 10        | Start-up timing diagram                                                    | 58 |

| Fig. 11        | Shutdown timing diagram                                                    | 58 |

| Fig. 12        | Watchdog Blockdiagram                                                      | 73 |

| Fig. 13        | IPC/ML71F16-A101E (product image may vary)                                 | 74 |

| Fig. 14        | Bottom view of the IPC/ML71 (product image may vary)                       | 75 |

| Fig. 15        | Front view with connector markings (product image may vary)                | 78 |

| Fig. 16        | Side view with connector markings (product image may vary)                 | 78 |

| Fig. 17        | Side view with connector markings (option with mounted connectivity board) | 78 |

| Fig. 18        | Open side view with Reset button, battery and CFast                        | 82 |

| Fig. 19        | Open side view with Reset button, battery and CFast                        | 83 |

| Fig. 20        | BIOS setup main menu                                                       | 90 |

| Fig. 21        | System information                                                         | 91 |

| Fig. 22        | Advanced menu                                                              | 91 |

| Fig. 23 | Baseboard Peripherals sub menu      | 92 |

|---------|-------------------------------------|----|

| Fig. 24 | SIO sub menu                        | 92 |

| Fig. 25 | UART configuration options          | 93 |

| Fig. 26 | Security menu                       | 93 |

| Fig. 27 | Boot menu                           | 94 |

| Fig. 28 | Exit menu                           | 94 |

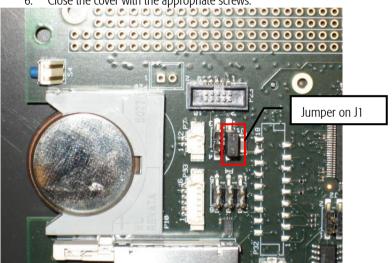

| Fig. 29 | Jumper on J1 :1-2 for BIOS recovery | 95 |

|         |                                     |    |

# 1 Introduction

# 1.1. General remarks

The content and presentation of this document has been carefully checked. No responsibility is accepted for any errors or omissions in the documentation.

Note that the documentation for the products is constantly revised and improved. The right to change this documentation at any time without notice is therefore reserved.

Syslogic is grateful for any help referring to errors or for suggestions for improvements.

The following registered trademarks are used:

| IBM-PC, PC/AT, PS/2       | trademarks of IBM Corporation      |

|---------------------------|------------------------------------|

| I <sup>2</sup> C          | trademark of Philips Corporation   |

| CompactFlash              | trademark of SanDisk Corporation   |

| PC/104                    | trademark of PC/104 Consortium     |

| PCI/104                   | trademark of PC/104 Consortium     |

| Intel Atom                | trademark of Intel Corporation     |

| Windows Embedded Compact  | trademark of Microsoft Corporation |

| Windows Embedded Standard | trademark of Microsoft Corporation |

All other trademarks appearing in this document are the property of their respective company.

# 1.2. Contents of this documentation

This document addresses to system integrators, programmers and instructed installation and maintenance personal working with the system. It provides all information needed to configure, setup and program the IPC/ML71xxx-xxxE systems.

# 1.3. Naming conventions

Throughout this documentation the product is referenced through it's marketing name "IPC/ML71". The same applies to the integrated base board. Throughout this documentation it will be referenced as "IPC/BL71".

# 1.4. Additional products and documents

## 1.4.1. Software products

There are no additional software products except operating systems:

- Operating Systems: check chapter 6.4 for a list of supported implementations.

# 1.5. Documents and references

## 1.5.1. Syslogic documentation

- CPU module documentation: DOC/ATOME6-E (cem\_atome6\_e.pdf)

## 1.5.2. Standards and books

The following documents are *useful* for additional information about PC/104 and IEEE 996.1:

- PC/104 Specification Version 2.3

- PCI/104 Specification Version 1.0

# IPC/ML71xxx-xxxE: user documentation DOC/COMPACT71-MLE; V1.3

- IEEE 996: IEEE standard document 'Personal Computer Bus Standard'

- IEEE 996.1: IEEE standard document 'Compact Embedded-PC Modules'

The PC/104 Specification may be downloaded from the Internet (see address below).

PC/104 Consortium <u>www.pc104.org</u>

The IEEE standard documents may be ordered directly from the IEEE or any standards document distributor (see addresses below).

- IEEE Standards Department www.ieee.org

- 'ISA & EISA, Theory and Operation' by Edward Solari (Annabooks, San Diego), ISBN 0-929392-15-9

- 'PCI System Architecture' by Tom Shanley / Don Anderson (Mindshare, Inc.), ISBN 0-201-30974-2

#### 1.5.3. Datasheets

For additional and more detailed information on the Intel Atom processor and chipset the following documents are of interest:

- Datasheet Intel Atom Processor E6xx Series

<u>http://download.intel.com/embedded/processor/datasheet/324208.pdf#iid=3790</u>

- Specification Update Intel Atom Processor E6xx Series

<a href="http://download.intel.com/embedded/processor/specupdate/324209.pdf?iid=3876#iid=3876#iid=3876">http://download.intel.com/embedded/processor/specupdate/324209.pdf?iid=3876#iid=3876</a>

- Datasheet Intel Platform Controller Hub EG20T(PCH) <u>http://download.intel.com/embedded/chipsets/datasheet/324211.pdf#iid=3791</u>

- Specification Update Intel Platform Controller Hub EG20T (PCH) <u>http://download.intel.com/embedded/processor/specupdate/324209.pdf?iid=3876#iid=3876</u>

- Datasheet Intel 82574 GbE Controller Family <u>http://download.intel.com/design/network/datashts/82574.pdf</u>

- Datasheet NXP SJA1000 <u>http://www.nxp.com/documents/data\_sheet/SJA1000.pdf</u>

- Application Note AN97076: SJA1000 Stand-alone CAN controller <u>http://www.nxp.com/documents/application\_note/AN97076.pdf</u>

## 1.6. Items delivered

- Will be inserted in a future release of this document.

# 1.7. Safety recommendations and warnings

The products are intended for measurement, control and communications applications in industrial environments. The products must be assembled and installed by specially trained people. The strict observation of the assembly and installation guidelines is mandatory.

The use of the products in systems in which life or health of persons is directly dependent (e.g. life support systems, patient monitoring systems, etc.) is not allowed.

The use of the products in potentially explosive atmospheres requires additional external protection circuitry which is not provided with the products.

In case of uncertainty or of believed errors in the documentation please immediately contact the manufacturer (address see chapter 11). Do not use or install the products if you are in doubt. In any case of misuse of the products, the user is solely liable for the consequences.

#### **Important note**

Ensure that the power supply is disconnected from the device before working on the device (connecting interfaces, replacing flash cards, batteries, opening the enclosure, etc.).

#### Important note

Please read the safety instructions of the power supply before installing/connecting the device.

1.7.1. EMC

#### Important note

This is a Class A product and not intended to be used in domestic environments. The product may cause electromagnetic interference. Appropriate measures must be taken.

#### 1.7.1. Battery

#### **Important note**

Caution! Danger of explosion if the battery is incorrectly replaced. Replace only with the same or equivalent type recommended by the manufacturer.

Dispose of used batteries according to the manufacturer's instructions.

## 1.7.2. Hot surface

#### **Important note**

Do not touch the surface of the device during operation. It may be hot and cause burns.

## 1.8. Electro-static discharge

Electronic boards are sensitive to Electro-Static Discharge (ESD). Please ensure that the product is handled with care and only in an ESD protected environment. Otherwise a proper operation is not guaranteed and the warranty is not applicable.

## 1.9. Life cycle information

#### 1.9.1. Transportation and storage

During transportation and storage the products must be in their original packing. The original packing contains a box with antistatic and shockabsorbing material. It is recommended, to keep the original packing in case of return of the product to the factory for repair. Note that the packing is recyclable.

#### 1.9.2. Operation

The operating environment must guarantee the environmental parameters (temperature, power supply, etc.) specified in the technical specification section of the product manuals.

The main functionality of the IPC system is defined by the application programs running on the processor board. The operating system and application programs are not part of the delivery by Syslogic but are defined, developed and tested by the customer or a system-integrator for each specific application. Refer to the respective documentation for more information.

#### 1.9.3. Maintenance and repair

The IPC system features error- and malfunction-detection circuitry. Diagnostic information gathered is transferred to the applications software where it can be used. In the rare case of a module hardware-failure or malfunction, the complete board should be exchanged. The faulty board must be returned to the factory for repair. Please use whenever possible the original packing for return of the product (ESD and mechanical protection).

### 1.9.4. Warranty

Our products are covered by a world-wide manufacturer's warranty. The warranty period starts at the delivery time from our official distributor to the customer. The duration of the warranty period is specified in the respective product catalogs and the offers. All products carry a serial number for identification. The manufacturing data and deliveries are registered in a high level Quality Management System.

The warranty covers material and manufacturing defects. All products must be returned via the official distributor to the factory for repair or replacement. The warranty expires immediately if the products are damaged of operation outside of the specified recommended operating conditions. The warranty also expires if the date code or job number listed on the product is altered or rendered unintelligible. The warranty does not include damage due to errors in firmware or software delivered with the products.

#### 1.9.5. RoHS

The products of the IPC/ML71 family are designed and produced according to the Restriction of Hazardous Substances (RoHS) Directive (2011/65/EC).

#### 1.9.6. Disposal and WEEE

At the end of the life span the IPC products must be properly disposed. IPC products contain a multitude of elements and must be disposed like computer parts. Some of the IPC products contain batteries which should be properly disposed.

The products of the IPC/ML71 are not designed ready for operation for the end-user and intended for consumer applications. Therefore the Waste Electrical and Electronic Equipment (WEEE) Directive (2002/96/EC) is not applicable. But users should still dispose the product properly at the end of life.

# 2 **Product description**

## 2.1. IPC/ML71 Systems

The IPC/ML71 contains an enclosure and the IPC/BL71 motherboard. A list of main features can be found in the table below:

# 2.2. Features

## 2.2.1. CPU core

- Intel Atom E680T (Tunnelcreek) single core processor for mobile devices

- industrial temperature range (-40..+85C)

- IA32 processor based on Intel's 45nm Hi-k metal gate silicon technology

- Multiple micro-ops per instruction are combined into one micro-op and executed in a single cycle

- in-order execution core

- high performance 32-bit 16-stage pipeline

- energy efficient branch prediction

- 1.6GHz processor clock

- 32kB, 4-way instruction and 24kB, 6-way data L1 cache with parity

- 512kB, 8-way L2 cache with ECC

- 32-bit wide DDR SDRAM interface

- supports Intel Hyper Threading Technology (HTT), 2 threads

- supports Intel Virtualization Technology (VT-x)

- supports Enhanced Intel Speedstep Technology

- PCIe as front side bus, 2.5GB/s, 1.0a Base Specification compliant (4 x1 lanes)

## 2.2.2. Memory

- up to 2048 Mbyte DDR2 SDRAM on board (device width x16)

- 800MT/s data rate

- 32bit data width

## 2.2.3. Graphics controller

- integrated Intel Graphics Media Accelerator 600 (Intel GMA600)

- power optimized 2D/3D graphics engine (max. 400MHz)

- integrated graphics device (IGD) includes LVDS and SDVO display ports

- LVDS max pixel clock 79.5MHz (equates to 1280x768 @ 85Hz)

- SDVO max. pixel clock 160MHz (equates to 1280x1024 @ 85Hz)

- Supports Streaming SIMD Extensions 2 and 3 (SSE2 and SSE3)

- Supports full hardware acceleration for H.264, MPEG2, MPEG4, VC1 and WMV9

- high performance 2D 64-bit graphics controller with backwards compatibility to VGA and SVGA standards

## 2.2.4. CFast and SATA interface

- CFast connector for onboard mountable CFast card

- standard SATA connector

### 2.2.5. Integrated peripherals

- integrated peripheral controller (IPC) with PC/AT compatible DMA controllers (2 x 8237), interrupt controllers (2 x 8259) and timer/counter channels (8254)

- hardware watchdog configurable for 100 ms or 1.6 s timeout, hardware reset activation

- temperature supervisor for software controlled power management

#### 2.2.6. PS/2 mouse and keyboard interface

- PC/AT compatible keyboard controller (8242 compatible) with PS/2 mouse support

- only available on an internal header

## 2.2.7. Serial ports

- six serial RS232 ports (COM1 COM6) with 16 byte receive and transmit FIFO (16550)

- optionally COM4 as a non-isolated, half-duplex RS485 interface

- optionally COM5 as an isolated, half-/full-duplex RS485 interface

- optionally COM6 as an isolated, half-/full-duplex RS485 interface

#### 2.2.8. Universal serial bus

- four USB V2.0 ports (OHCI/EHCI-Host Controller) on a standard USB connector

- two USB V2.0 ports (OHCI/EHCI-Host Controller) on internal header

#### 2.2.9. Ethernet

- Up to three 10/100/1000 baseT Ethernet interfaces

### 2.2.10. Firmware flash memory

- 8 MBit BootBlock Flash for BIOS and setup data (excluding date and time)

#### 2.2.11. Real time clock

- year 2000 compliant Real Time Clock (PC/AT compatible)

- battery backed through onboard battery or header

#### 2.2.12. Configuration switches

- rotary hex switch for customer application

## 2.2.13. SPI

- SPI interface on internal header

- up to 8MB flash size allowed

#### 2.2.14. SMBus (I2C)

- SMBus v1.0 compliant (3.3V CMOS)

- SMBus interface on internal header

#### 2.2.15. HDA/SPKR

- HDA/SPKR interface on internal header

## 2.2.16. LPC

- LPC 1.1 compliant interface

- LPC interface on internal header

## 2.2.17. Power Supply

- onboard non-isolated power supply with wide input range (10Vdc ... 30Vdc)

- configurable power supply supervision (this function is only available on systems with revision 2 or higher)

- monitors either external power supply voltage or it can be used as external power fail or on/off input (this function is only available on systems with revision 2 or higher)

- optional isolated power supply

## 2.2.18. PC/104 Bus Interface

- Subset of standard PC/104 bus interface

- DIN41612 bus connector

## 2.2.19. CAN Interface

- Two SJA1000 stand-alone CAN controller from NXP (Philips Semiconductor)

- BasicCAN or PeliCAN mode

- supports CAN 2.0A protocol in BasicCAN mode

- supports CAN 2.0B protocol in BasicCAN mode (29 bit identifier accepted)

- sully supports CAN 2.0B protocol in PeliCAN mode

- 16MHz clock frequency

- fixed I/O base addresses

- uses IRQ15

- ISO 11898-24V compatible interface

- optical isolation (1000VDC)

- configurable termination resistor

- standard CAN-OUT DSUB9 connector

- optionally CAN-IN DSUB9 connector

# IPC/ML71xxx-xxxE: user documentation DOC/COMPACT71-MLE; V1.3

Fig. 1 Block diagram (IPC/ML71)

| Gerät             | IPC/ML71F16-<br>A101E     | IPC/ML71F16-<br>A102E     |                   |                   |                   |                   |                   |

|-------------------|---------------------------|---------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| Function<br>Board | IPC/BL71-<br>101E         | IPC/BL71-<br>102E         | IPC/BL71-<br>103E | IPC/BL71-<br>104E | IPC/BL71-<br>105E | IPC/BL71-<br>107E | IPC/BL71-<br>109E |

| ETH1              | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| ETH2              | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| ETH3              | Х                         |                           |                   |                   |                   | Х                 |                   |

| RGMII             |                           |                           |                   |                   |                   |                   |                   |

| COM1              | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| COM2              | Х                         | Х                         | (X)               | (X)               | (X)               | (X)               | (X)               |

| COM3              | Х                         | Х                         |                   |                   | (X)               |                   | (X)               |

| COM4              | (X)                       | Х                         | (X) RS485         |                   | (X)               |                   | (X)               |

| COM5              | (X)                       | (X)                       |                   |                   |                   |                   | (X)               |

| COM6              | Х                         | (X)                       | (X) RS485         |                   |                   |                   | (X)               |

| CAN1              | Х                         | Х                         | Х                 |                   |                   |                   |                   |

| CAN2              |                           | Х                         |                   |                   |                   |                   |                   |

| USB0/1            | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| USB2/3            | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| USB4/5            | (X)                       | (X)                       | (X)               | (X)               | (X)               | (X)               |                   |

| USB Device        |                           |                           |                   |                   |                   |                   |                   |

| DVI               | Х                         | Х                         | Х                 |                   | Х                 | Х                 | Х                 |

| VGA               |                           |                           |                   |                   |                   |                   |                   |

| LVDS              | (X)                       |                           | (X)               | (X)               |                   |                   |                   |

| Inverter          |                           |                           | (X)               | (X)               |                   |                   |                   |

| CFast             | Х                         | Х                         | Х                 | X                 | Х                 | Х                 | Х                 |

| SATA              | (X)                       | (X)                       | (X)               | (X)               | (X)               | (X)               |                   |

| SPI               | (X)                       |                           | (X)               | (X)               | (X)               | (X)               |                   |

| I2C               | (X)                       |                           | (X)               | (X)               | (X)               | (X)               |                   |

| HDA/SPKR          | (X)                       |                           | (X)               | (X)               | (X)               | (X)               |                   |

| LPC               | (X)                       |                           | (X)               |                   |                   | (X)               |                   |

| ISA Bus           | (X)                       |                           |                   |                   |                   |                   |                   |

| Reset Button      | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| Rotary Switch     | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| ,<br>Temp. sensor | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| Watchdog          | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| PM Controller     | Х                         | Х                         | Х                 | Х                 | Х                 | Х                 | Х                 |

| Battery/GoldCap   | BAT                       | BAT                       | BAT               | BAT               | BAT               | CAP               | BAT               |

| CPU               | E680T/EG20T<br>1.6GHz/1GB | E680T/EG20T<br>1.6GHz/1GB | n/a               | n/a               | n/a               | n/a               | n/a               |

# 2.3. **Product Variants**

### Tab. 1 Feature List

(X) means that the interface is only available on an internal header. Please refer to the following chapter for a more detailed description of the interface and its connector.

# 3 Hardware description

## 3.1. Overview

The IPC/IPC/BL71 board hardware may be configured by software (BIOS) and by jumper setting. Software configuration should always be done by using the BIOS Setup. The BIOS Setup can be entered by pressing <F2> at power-up. The jumper and connector locations are shown in the board layout drawing (Fig. 3).

#### **Important Note**

Always check the jumper configuration of a freshly received board to comply with your system requirements before applying power, otherwise the system may get damaged or may fail to operate.

Fig. 2 Board layout (IPC/BL71)

| Connector<br>/Header<br>ID | Туре                                           | Comment                 |  |  |

|----------------------------|------------------------------------------------|-------------------------|--|--|

|                            | 1x4pin, Rm3.81, 90                             |                         |  |  |

| P1                         | Weidmüller SC-SMT 3.81/04/90 LF RL (186398000) | Power Supply            |  |  |

|                            | 220pin SMX                                     | CoreExpress             |  |  |

| P2                         | Тусо 3-1827253-6                               | Bottom side             |  |  |

|                            | 2x10pin, Rm1.25                                |                         |  |  |

| P3                         | Hirose DF13A-20DP-1.25V                        | LVDS                    |  |  |

|                            | 2x3pin Header, Rm2.54                          |                         |  |  |

| P4                         | Harwin M20-8760342                             | LDDC Programming Header |  |  |

| Dr                         | DVI                                            |                         |  |  |

| P5                         | Molex 74320-1004                               | DVI                     |  |  |

| DC                         | 6pin PicoBlade, Rm1.25<br>Molex 53398-0671     | CMDue                   |  |  |

| P6                         | 2pin PicoBlade, Rm1.25                         | SMBus                   |  |  |

| P7                         | Molex 53398-0271                               | Speaker                 |  |  |

| Γ/                         | SATA Plug, Rm1.27                              |                         |  |  |

| P8                         | Molex 67800-5002                               | SATA                    |  |  |

| 10                         | 1x2pin Micro-Fit Header, Rm3.0                 |                         |  |  |

| P9                         | Molex 43650-0226                               | SATA                    |  |  |

|                            | Battery Holder                                 |                         |  |  |

| P10                        | ,<br>Renata NL 5077-LF                         | Battery                 |  |  |

| D11                        | 2x6pin PC/104 non stack through, press fit     |                         |  |  |

| P11                        | avenin DC/104 non stack through prossifit      | ISA Bus                 |  |  |

| P12                        | 2x6pin PC/104 non stack through, press fit     | ISA Bus                 |  |  |

| P 12<br>PA/PB              | 2x32pin PC/104 non stack through, press fit    | ISA Bus                 |  |  |

| PC/PD                      | 2x20pin PC/104 non stack through, press fit    | ISA Bus                 |  |  |

| PA/PB/PC/ P                | DIN41612 Style C, Rm2.54                       |                         |  |  |

| D                          | Elco 21 8458 128 031 025                       | ISA Bus                 |  |  |

|                            | 6pin MiniDIN                                   |                         |  |  |

| P13                        | Kycon KMDGX-6S-BS                              | PS/2                    |  |  |

|                            | DSUB9, DIN41652                                |                         |  |  |

| P14                        | Harting 09 66 162 681 2                        | COM1                    |  |  |

|                            | 2x2pin Datamate, Rm2.0                         |                         |  |  |

| P15                        | Harwin M80-82 8 04 45 P                        | USB Port 4              |  |  |

|                            | 2x2pin Datamate, Rm2.0                         |                         |  |  |

| P16                        | Harwin M80-82 8 04 45 P                        | USB Port 5              |  |  |

|                            | RJ45 with int. Magnetics, Gigabit              |                         |  |  |

| P17                        | Тусо 2-1840408-6                               | ETH1                    |  |  |

|                            | RJ45 with int. Magnetics, Gigabit              |                         |  |  |

| P18                        | Tyco 2-1840408-6                               | ETH2                    |  |  |

| Dio                        | RJ45 with int. Magnetics, Gigabit              |                         |  |  |

| P19                        | Tyco 2-1840408-6                               | ETH3                    |  |  |

| Dao                        | Double USB Type A                              |                         |  |  |

| P20                        | Kycon KUSBX-A2N-B                              | USB0/1                  |  |  |

| Connector<br>/Header<br>ID | Туре                       | Comment                |

|----------------------------|----------------------------|------------------------|

|                            | Double USB Type A          |                        |

| P21                        | Kycon KUSBX-A2N-B          | USB2/3                 |

|                            | 2x5pin Header, Rm2.54      |                        |

| P23                        | FCI 20021521-00010D4LF     | HDA                    |

|                            | 6pin PicoBlade, Rm1.25     |                        |

| P24                        | Molex 53398-0671           | Backlight              |

|                            | 2x6pin Dubox, Rm2.54       |                        |

| P26                        | FCI 89898-306ALF           | SATA                   |

|                            | CompactFlash Type I, 50pin |                        |

| P27                        | 3M N7G24-A0B2-RB-10-OHT    | CFast                  |

|                            | 7pin PicoBlade, Rm1.25     |                        |

| P28                        | Molex 53398-0771           | PIC Programming Header |

|                            | 2pin Header, Rm2.54        |                        |

| P29                        | JST B 2B-XH-A              | Battery Header         |

|                            | DSUB9, DIN41652            |                        |

| P30                        | Harting 09 66 162 681 2    | CAN1                   |

|                            | DSUB9, DIN41652            |                        |

| P31                        | Harting 09 66 162 681 2    | CAN2                   |

|                            | 18pin Picoflex             |                        |

| P32                        | Molex 90816-0318           | RGMII                  |

|                            | 6pin PicoBlade, Rm1.25     |                        |

| P33                        | Molex 53398-0671           | SPI                    |

Tab. 2List of connectors

| Connector/ |                             |                        |

|------------|-----------------------------|------------------------|

| Header ID  | Туре                        | Comment                |

|            | 2x2pin Header, Rm2.54       | BIOS INIT#             |

| J1         | Samtec TSM-102-01-L-DV-P-TR | BIOS DISABLE#          |

|            | 2x2pin Header, Rm2.54       |                        |

| J2         | Samtec TSM-102-01-L-DV-P-TR | Watchdog Timeout       |

|            | 1x8pin Header, Rm2.54       |                        |

| J3         | Harwin M20-8770842          | LPC                    |

|            | 1x6pin Header, Rm2.54       |                        |

| J4         | Harwin M20-8770642          | JTAG                   |

|            | 2x5pin Header, Rm2.54       |                        |

| J6         | Samtec TSM-105-01-L-DV-P-TR | PS/2                   |

|            | 2x5pin Header, Rm2.54       |                        |

| J7         | Samtec TSM-105-01-L-DV-P-TR | COM2                   |

|            | 2x5pin Header, Rm2.54       |                        |

| J8         | Samtec TSM-105-01-L-DV-P-TR | COM3                   |

|            | 2x5pin Header, Rm2.54       |                        |

| J9         | Samtec TSM-105-01-L-DV-P-TR | COM4                   |

|            | 2x5pin Header, Rm2.54       |                        |

| J10        | Samtec TSM-105-01-L-DV-P-TR | COM5                   |

|            | 2x5pin Header, Rm2.54       |                        |

| J11        | Samtec TSM-105-01-L-DV-P-TR | COM6                   |

|            | 4pin PicoBlade, Rm1.25      |                        |

| J13        | Molex 53398-0471            | Power Supply           |

|            | 2x2pin Header, Rm2.54       |                        |

| J16        | Samtec TSM-102-01-L-DV-P-TR | Shield/GND Connection  |

|            | 2x3pin Header, Rm2.54       |                        |

| J18        | Harwin M20-8760342          | DDC Programming Header |

|            | 1x3pin Header               | Battery Activation     |

| J19        | Samtec TSM-103-01-L-SH-P-TR | Bottom side            |

|            | 2x2pin Header, Rm2.54       |                        |

| J21        | Samtec TSM-102-01-L-DV-P-TR | CAN1                   |

|            | 2x2pin Header, Rm2.54       |                        |

| J22        | Samtec TSM-102-01-L-DV-P-TR | CAN2                   |

Tab. 3List of headers

| Connector/H | I                                 |                         |

|-------------|-----------------------------------|-------------------------|

| eader ID    | Туре                              | Comment                 |

|             | Switch                            |                         |

| S4          | Bourns 7914S                      | Reset Button            |

|             | 2pin DIL Switch                   |                         |

| S5          | Copal CHS-02B                     | COM4 (RS485)            |

|             | Rotary coded Switch, 16 positions |                         |

| S9          | Copal S-7050ETA                   | Rotary Hex Switch       |

|             | 2pin DIL Switch                   | External On/Off         |

| S12         | Copal CHS-02B                     | Power Fail              |

|             | Rotary coded Switch, 16 positions |                         |

| S14         | Copal S-7050ETA                   | Power Management Mode   |

|             | 2pin DIL Switch                   |                         |

| S15         | Copal CHS-02B                     | PWM Mode                |

|             | 2pin DIL Switch                   |                         |

| S16         | Copal CHS-02B                     | LVDS Configuration      |

|             | 2pin DIL Switch                   |                         |

| S17         | Copal CHS-02B                     | CAN1/COM5 Configuration |

|             | 2pin DIL Switch                   | CAN2/COM6               |

| S18         | Copal CHS-02B                     | Configuration           |

|             | 2pin DIL Switch                   |                         |

| S19         | Copal CHS-02B                     | COM5 Half/Full Duplex   |

|             | 2pin DIL Switch                   |                         |

| S20         | Copal CHS-02B                     | COM6 Half/Full Duplex   |

Tab. 4 List of switches

## 3.2. Memory and I/O resources

#### 3.2.1. General memory layout and configuration

The IPC/BL71 uses the same memory layout as a standard desktop PC. Onboard devices, DRAM, graphics controller and Boot Block Flash make use of the 4 GByte addressable memory space. Tab. 5 shows a typical configuration of the IPC/BL71

| Ad         | dress        | Size | Device / Register           | Remarks |

|------------|--------------|------|-----------------------------|---------|

| 0000'0000h | - 0009'FFFFh | 640K | Main Memory (DRAM)          |         |

| 000A'0000h | - 000B'FFFFh | 128K | Embedded Media and Graphics |         |

|            |              | _    | Driver Function 0           |         |

| 000C'0000h | - 000D'FFFFh | 128K | System Board                |         |

| 000E'0000h | - 000E'FFFFh | 64K  | System Board                |         |

| 000F'0000h | - 000F'FFFFh | 64K  | System Board                |         |

| 7F70'0000h | - 7F7F'FFFFh | 1 M  | System Board                |         |

| 7F80'0000h | - 7FFF'FFFFh | 8M   | System Board                |         |

| 8000'0000h | - FFFF'FFFFh | 2G   | PCI Bus                     |         |

Tab. 5

Physical Memory Address Space Layout for IPC/ML71

#### Important note

The main memory above 1M isn't fully usable for applications. The main memory for applications is shared with the graphics memory (UMA: Unified Memory Architecture).

BIOS and other System devices use memory above 1MB. Depending on enabled or disabled functions in the BIOS the amount of additional memory used can vary.

# IPC/ML71xxx-xxxE: user documentation DOC/COMPACT71-MLE; V1.3

Fig. 3 Memory map

## 3.2.2. General I/O Layout and configuration

The IPC/BL71's 64 kbyte I/O address space is mapped to the PC/104 bus address space as indicated in the table below. Note that 16 bit address decoding should be used on all PC/104 expansion boards to make efficient use of the I/O address space.

| Add   | ress    | Size     | Device / Register | Remarks           |

|-------|---------|----------|-------------------|-------------------|

| 0000h | - 000Fh | 16 Bytes | Slave DMA (8237)  |                   |

| 0020h | - 0021h | 2 Bytes  | PIC master (8259) | command/status    |

| 0040h | - 0043h | 4 Bytes  | PIT (8254)        |                   |

| 0060h | -       | 1 Byte   | Keyboard/mouse    | data port         |

| 0061h | -       | 1 Byte   | Port B            | control           |

| 0064h |         | 1 Byte   | keyboard/mouse    | command/status    |

| 0070h | - 0071h | 2 Bytes  | RTC RAM           | address/data port |

# IPC/ML71xxx-xxxE: user documentation DOC/COMPACT71-MLE; V1.3

| 0072h           | - | 0073h  | 2 Bytes              | high RTC RAM           | address/data port      |

|-----------------|---|--------|----------------------|------------------------|------------------------|

| 0080h           |   | 007511 | 1 Byte               | POST code              |                        |

| 0081h           | _ | 0083h  | 2 Bytes              | DMA (8237)             |                        |

| 0087h           |   | 000511 | 1 Byte               | DMA (8237)             |                        |

| 0089h           | _ | 008Bh  | 3 Bytes              | DMA (8237)             |                        |

| 0089M           | - | UUUU   | 1 Byte               | DMA (8237)             |                        |

| 0092h           | - |        |                      | Port A                 |                        |

| 009211<br>00A0h | - | 00BFh  | 1 Byte               | PIC slave (8259)       | Command/Status         |

| 00A01           | - | 00DF   | 32 Bytes<br>32 Bytes | DMA (8237)             | Command/Status         |

|                 | - | UUDF   |                      |                        |                        |

| 00F0h           |   |        | 1 Byte               | Numeric Data Processor |                        |

| 00C4            |   | 0225   | 40 Dutes             | Free                   | avail On DC/104 hus    |

| 0200h           | - | 022F   | 48 Bytes             |                        | avail. On PC/104 bus   |

| 0278            | - | 027Fh  | 16 Bytes             | reserved for LPT2      |                        |

| 02A8h           | - | 02Afh  | 8 Bytes              | COM6                   |                        |

| 02E0            | - | 02Efh  | 16 Bytes             | free                   | avail. On PC/104 bus   |

| 02F8            | _ | 02FFh  | 8 Bytes              | COM2                   |                        |

| 0300h           | - | 036Fh  | _                    | free                   | avail. On PC/104 bus   |

| 0370h           | _ | 0372h  | 3 Bytes              | reserved for Floppy 2  | Legacy, not available  |

| 0374h           | - | 0375h  | 2 Bytes              | reserved for Floppy 2  | Legacy, not available  |

| 0377h           |   |        | 1 Bytes              | reserved for Floppy 2  | Legacy, not available  |

| 0378h           | - | 037Fh  | 8 Bytes              | reserved for LPT2      | Legacy, not available  |

| 03A8h           | - | 03Afh  | 8 Bytes              | COM5                   |                        |

| 03B0h           | - | 03BBh  | 11 Bytes             | VGA adapter            |                        |

| 03BCh           | - | 03BFh  | 4 Bytes              | reserved for LPT3      | Legacy, not available  |

| 03C0h           | - | 03CFh  | 8 Bytes              | VGA adapter            | EGA                    |

| 03D0h           | - | 03DFh  | 8 Bytes              | VGA adapter            | CGA                    |

| 03E0h           | - | 03EFh  | 16 Bytes             | free                   | avail. On PC/104 bus   |

| 03F0h           | - | 03F2h  | 3 Bytes              | reserved for Floppy 1  | Legacy, not available  |

| 03F4h           | - | 03F5h  | 2 Bytes              | reserved for Floppy 1  | Legacy, not available  |

| 03F6h           |   |        | 1 Byte               | primary IDE channel    | Legacy, not available  |

| 03F7h           |   |        | 1 Byte               | reserved for Floppy 1  | Legacy, not available  |

| 03F8h           | - | 03FFh  | 8 Bytes              | COM1                   |                        |

| 0481h           | - | 0483h  | 2 Bytes              | DMA high page          |                        |

| 0487h           |   |        | 1 Bytes              | DMA high page          |                        |

| 0489h           | - | 048Bh  | 3 Bytes              | DMA high page          |                        |

| 048Fh           |   |        | 1 Byte               | DMA high page          |                        |

| 04D0h           | - | 04D1h  | 2 Bytes              | PIC                    | Level/Edge             |

| 0500h           | - | 07FFh  | 2048 Bytes           | runtime registers SIO  | Refer to Datasheet     |

| 0A78h           |   |        | 1 Byte               | PnP                    | Configuration port     |

| 0CF8h           | - | 0CFFh  | 8 Bytes              | PCI                    | Configuration register |

| 2000h           | - | 2FFF   | 4096 Bytes           | PCI-PCI bridge         |                        |

| 3000h           | - | 3FFFh  | 4096 Bytes           | PCI-PCI bridge         |                        |

| 4000h           | - | 401Eh  | 29 Bytes             | USB controller         |                        |

| 4020h           | - | 403Eh  | 29 Bytes             | USB controller         |                        |

| 4040h           | - | 405EH  | 29 Bytes             | USB controller         |                        |

| 4060h           | _ | 406Eh  | 15 Bytes             | IDE controller         |                        |

| 4070h   | - | 4076h   | 7 Bytes    | VGA controller            |                      |

|---------|---|---------|------------|---------------------------|----------------------|

| 7600h   | - | 76FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 7600h   | - | 76FFh   | 256 Bytes  | CAN1                      |                      |

| 7700h   | - | 77FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 7700h   | - | 77FFh   | 256 Bytes  | CAN2                      |                      |

| 7800h   | - | 7FFFh   | 2048 Bytes | Free                      | avail. On PC/104 bus |

| 8000h   | - | 80FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8100h   | - | 81FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8200h   | - | 821Fh   | 16 Bytes   | IPC/BL71 system registers |                      |

| 8220h   | - | 82DFh   | 192 Bytes  | free                      | avail. on PC/104 bus |

| 8300h   | - | 83FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8400h   | - | 84FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8500h   | - | 85FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8600h   | - | 8600h   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8700h   | - | 87FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8800h   | - | 88FFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8900h   | - | 8900h   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8A00h   | - | 8AFFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8B00h   | - | 8BFFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8C00h   | - | 8CFFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8D00h   | - | 8DFFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8E00h   | - | 8EFFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 8F00h   | - | 8FFFh   | 256 Bytes  | Free                      | avail. On PC/104 bus |

| 0'D000h | - | 0'EFFFh | 1024 Bytes | Reserved for PCI device   | VGA, LAN, USB, IDE   |

Tab. 6I/O address space layout

Only the I/O addresses which are marked with "avail. On PC/104 bus" can be accessed on the aforementioned connector and be used for additional peripherals. The other unused I/O space can't be accessed because these cycles are claimed by the integrated South Bridge and not by the PCI/ISA Bridge.

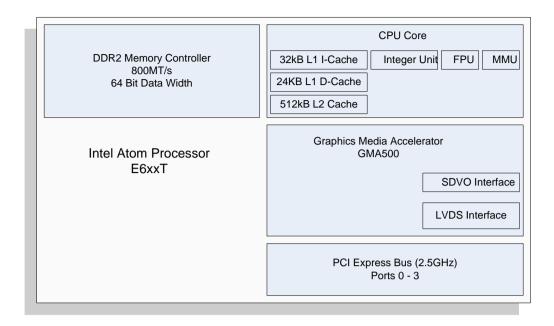

## 3.3. Intel Atom E6xxT Processor

The Intel Atom E6xx Processor Family (Codename Tunnelcreek) is a highly integrated x86 processor for embedded applications.

# IPC/ML71xxx-xxxE: user documentation DOC/COMPACT71-MLE; V1.3

Fig. 4 Intel Atom Processor E6xx

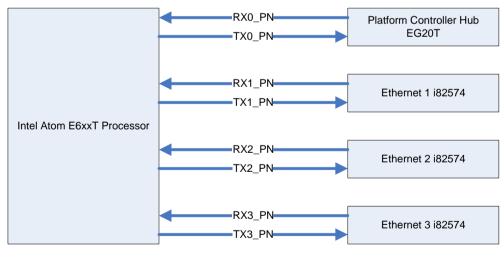

# 3.4. PCI/PCIe devices

All devices follow the PCI 2.2 and PCIe 1.0a specification. The BIOS (and/or OS) controls memory and I/O resources.

PCIe Lanes

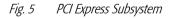

# 3.5. Intel Platform Controller Hub EG20T

The Intel Platform Controller Hub EG20T companion device (Codename Top Cliff) is designed to work with the Atom E6xx processor. The Platform Controller Hub is connected to the CPU using a PCIe lane.

Fig. 6 Intel Platform Controller Hub EG20T

| PCI Device            | Vendor ID | Device ID | Bus/<br>Device/ | Interrupt Pin<br>INTline | Comment    |

|-----------------------|-----------|-----------|-----------------|--------------------------|------------|

|                       |           |           | Function        | INTINC                   |            |

| Intel Host Controller | 8086      | 4114h     | 00/00/00        |                          |            |

| Intel Host Controller | 8086      | 8183h     | 00/01/00        |                          |            |

| Intel VGA Controller  | 8086      | 4108h     | 00/02/00        | A/16                     |            |

| Intel Video Device    | 8086      | 8182h     | 00/03/00        | A/11                     |            |

| PCI-to-PCI Bridge     | 8086      | 8184h     | 00/17/00        | A/16                     | PCle       |

| PCI-to-PCI Bridge     | 8086      | 8185h     | 00/18/00        | A/17                     | PCle       |

| PCI-to-PCI Bridge     | 8086      | 8180h     | 00/19/00        | A/18                     | PCle       |

| PCI-to-PCI Bridge     | 8086      | 8181h     | 00/1A/00        | A/19                     | PCle       |

| ISA Bridge            | 8086      | 8186h     | 00/1F/00        | -/-                      |            |

| PCI-to-PCI Bridge     | 8086      | 8800h     | 01/00/00        | A/16                     |            |

| Intel Controller      | 8086      | 8801h     | 02/00/00        | -/-                      | Packet Hub |

| GbE                   | 8086      | 8802h     | 02/00/01        | A/16                     |            |

| Controller            | 8086      | 8803h     | 02/00/02        | A/16                     | GPIO       |

| USB Host #1 (OHCl0)   | 8086      | 8804h     | 02/02/00        | B/19                     |            |

| USB Host #1 (OHCI1)   | 8086      | 8805h     | 02/02/01        | B/19                     |            |

| USB Host #1 (OHCl2)   | 8086      | 8806h     | 02/02/02        | B/19                     |            |

| USB Host #1 (EHCI)    | 8086      | 8807h     | 02/02/03        | B/19                     |            |

| USB Device            | 8086      | 8808h     | 02/02/04        | B/19                     |            |

| System Device         | 8086      | 8809h     | 02/04/00        | C/7                      | SDIO #0    |

| System Device         | 8086      | 880Ah     | 02/04/01        | C/7                      | SDIO #1    |

| AHCI Controller       | 8086      | 880Bh     | 02/06/00        | D/17                     | SATA II    |

| USB Host #0 (OHCl0)   | 8086      | 880Ch     | 02/08/00        | A/16                     |            |

| USB Host #0 (OHCI1)   | 8086      | 880Dh     | 02/08/01        | A/16                     |            |

| USB Host #0 (OHCl2)   | 8086      | 880Eh     | 02/08/02        | A/16                     |            |

| PCI Device         | Vendor ID | Device ID | Bus/     | Interrupt Pin | Comment        |

|--------------------|-----------|-----------|----------|---------------|----------------|

|                    |           |           | Device/  | INTline       |                |

|                    |           |           | Function |               |                |

| USB Host #0 (EHCI) | 8086      | 880Fh     | 02/08/03 | A/16          |                |

| Intel Controller   | 8086      | 8810h     | 02/10/00 | B/19          | DMA            |

| Serial Device      | 8086      | 8811h     | 02/10/01 | B/11          | UART #0        |

| Serial Device      | 8086      | 8812h     | 02/10/02 | B/11          | UART #1        |

| Serial Device      | 8086      | 8813h     | 02/10/03 | B/11          | UART #2        |

| Serial Device      | 8086      | 8814h     | 02/10/04 | B/11          | UART #3        |

| Intel Controller   | 8086      | 8815h     | 02/12/00 | C/7           | DMA            |

| Intel Controller   | 8086      | 8816h     | 02/12/01 | C/7           | SPI            |

| Intel Controller   | 8086      | 8817h     | 02/12/02 | C/18          | I2C            |

| CANbus Controller  | 8086      | 8818h     | 02/12/03 | C/18          | CAN            |

| Intel Controller   | 8086      | 8819h     | 02/12/04 | C/18          | IEEE1588 block |

#### Tab. 7 PCI devices EG20T

The interrupt resources are assigned automatically by the BIOS and can be modified through a special setup screen (see chapter 3.6).

## 3.6. Hardware interrupts

The Intel Atom processor E6xx chipset integrates two legacy 8259-compatible Programmable Interrupt Controllers (PIC). The registers of the PIC can be accessed through the I/O ports 020h and 021h resp. 0A0h and 0A1h.

| Device     | IRQ | PCI IRQ | Comment                   |

|------------|-----|---------|---------------------------|

| 8254 Timer | 0   | -       | Legacy                    |

| Keyboard   | 1   | -       | Legacy                    |

| 8259       | 2   | -       | Slave controller          |

| UART       | 3   | -       | COM2                      |

| UART       | 4   | -       | COM1                      |

| COM3       | 5   | -       | COM3                      |

| COM4       | 6   | -       | COM4                      |

| COM5       | 7   | -       | COM5 (if disabled no IRQ) |

| COM6       | 7   | -       | COM6 (if disabled no IRQ) |

| PCI        | 7   |         | Reserved for PCI devices  |

| RTC        | 8   | -       | Legacy                    |

| ACPI       | 9   | -       | Reserved                  |

| PCI        | 10  | -       | Reserved for PCI devices  |

| PCI        | 11  | -       | Reserved for PCI devices  |

| Mouse      | 12  | -       | Legacy                    |

| FPU        | 13  | -       | Legacy                    |

| IDE        | 14  | -       | Reserved for PCI devices  |

| CAN        | 15  | -       | CAN1 and CAN2             |

#### Tab. 8 Hardware interrupt table

The interrupt and PnP resource are automatically allocated by the BIOS. In the setup screen "*PnP/PCI Configurations*" each interrupt can be reserved for a special peripheral device. During startup the PCI bus enumeration won't assign a reserved interrupt to a PnP/PCI device.

## 3.7. DMA channels

| DMA | Data Width | System Resource                 |

|-----|------------|---------------------------------|

| 0   | 8 bits     | Available                       |

| 1   | 8 bits     | Available                       |

| 2   | 8 bits     | Available                       |

| 3   | 8 bits     | Available                       |

| 4   |            | Reserved, cascaded with channel |

| 5   | 16 bits    | Available                       |

| 6   | 16 bits    | Available                       |

| 7   | 16 bits    | Available                       |

Tab. 9 DMA channels

## 3.8. Peripheral devices

#### 3.8.1. Scope

The peripheral devices described in this chapter are the core features of the IPC/BL71 board. Meaning that they're available on all derivates. Special features implemented only on one special board are described in a separate chapter of this documentation.

### 3.8.2. DVI interface

The DVI (Digital Visual Interface) signals are available on the High Density DVI-D connector P5 for direct connection of DVI compatible monitors. The signals from the SDVO (Serial Digital Video Out) port are converter into DVI signals from the controller uses the standard VGA register interface. All configurations are done by software (BIOS, VGA-BIOS).

#### **Device connection**

| Pin Number | Signal     | Remarks          |

|------------|------------|------------------|

| 1          | DATA#2     |                  |

| 2          | DATA2      |                  |

| 3          | Shield 2/4 | Connected to GND |

| 4          | DATA#4     | Not connected    |

| 5          | DATA4      | Not connected    |

| 6          | DDC_CLK    |                  |

| 7          | DDC_DATA   |                  |

| 8          | NC         | Not connected    |

| 9          | DATA#1     |                  |

| 10         | DATA1      |                  |

| 11         | Shield 1/3 | Connected to GND |

| 12         | DATA#3     | Not connected    |

| 13         | DATA3      | Not connected    |

| 14         | VCC5       | +5Vdc            |

| 15         | GND        |                  |

| 16         | HPDET      | Hot Plug Detect  |

| 17         | DATA#0     |                  |

# IPC/ML71xxx-xxxE: user documentation DOC/COMPACT71-MLE; V1.3

| 18 | DATAO      |                  |

|----|------------|------------------|

| 19 | Shield 0/5 | Connected to GND |

| 20 | DATA#5     |                  |

| 21 | DATA5      |                  |

| 22 | Shield CLK | Connected to GND |

| 23 | CLK        |                  |

| 24 | CLK#       |                  |

|    |            |                  |

| C1 | VGA_RED    | Not connected    |

| C2 | VGA_GREEN  | Not connected    |

| C3 | VGA_BLUE   | Not connected    |

| C4 | HSYNC      | Not connected    |

| C5 | VGA_GND    | Not connected    |

Tab. 10 DVI-D connector P5

| Pin Number | Signal  | Remarks       |

|------------|---------|---------------|